利用Xilinx UltraScale架构大幅提升生产力

时间:01-12

来源:互联网

点击:

集成核心功能

高度灵活的可编程性这一极具价值的功能与诸多事情一样,要想有所得就要付出代价。利用可编程资源构建的功能可能比专门针对该功能的模块尺寸更大,甚至可能速度更慢。当然,FPGA本质上明显的优势就是具有可编程性,但赛灵思FPGA实现了专门功能、集成IP的

适当平衡,能帮助用户快实现常用功能(图3)。UltraScale架构包含针对常见通信协议的集成模块。Kintex UltraScale和Virtex UltraScale器件中包含针对PCI Express、100G Ethernet和150G Interlaken的多个集成模块,且都经过全面测试和验证,能确保实现功能。

除了通信协议之外,每个I/O Bank都包含一个可编程存储器PHY,能用存储器接口生成器(MIG)工具进行配置。这充分说明了根据需要进行集成的特性。存储器PHY和一些控制逻辑可创建为可编程专用函数,但存储器接口的数字部分用器件架构构建,针对不同模式提供所有必需的定制与支持,而这则是专门电路所难以实现的。

在器件架构中有大量其它模块,专门设计用于执行特定功能,同时保持可编程性。设计人员能以不同深度和广度来配置这些模块存储器,以级联成更大型的低功耗阵列。DSP Slice具有许多模式,能让用户根据所选功能访问模块的不同组件。因此除了门和寄存器之外,UltraScale架构上能实现大量丰富的功能。

可定制、可重复的IP能提高生产力

每个设计都包含许多不同架构构建块,相互连接构成系统。行业内有些功能已经非常完备了,从经济性角度讲完全可以将它们做成专用的固定功能模块。然而,最佳设计方法是采用可编程逻辑构建功能,并经过验证,随时按需重用。这种IP概念已经存在了很多代,但赛灵思近期推出了一些生产力增强特性(图4)。

图4 – Vivado工具加速复杂设计的创建和实现。

即插即用IP

2012年,赛灵思采用ARM®AMBA® AXI4接口作为即插即用IP的标准接口。采用统一的标准接口相比过去能大幅简化IP集成,将多种不同接口整合到一个,设计人员也不必去掌握多种不同的接口。UltraScale架构继续受益于AXI4互联的灵活性和可扩展性,从而帮助设计人员实现最快的产品上市进程,同时采用AXI4-Lite和AXI4-Stream等不同AXI4互联协议优化IP性能、面积和功耗。

Vivado IP Packager和IP Catalog采用IP-XACT标准(该标准最初由SPIRIT联盟作为工具流程中封装、集成和重用IP的标准结构推出)。IP-XACT现已获得IEEE的批准(IEEE1685-2009)。Vivado IP Packager采用在本地或共享驱动器上可扩展IP Catalog中提供的约束、测试平台和文档来创建设计。采用Vivado IP Catalog,用户能够将自己的IP、赛灵思的IP以及第三方IP无缝集成在一起,从而确保设计团队轻松一致地分享所有IP。

VIVADO IP INTEGRATOR

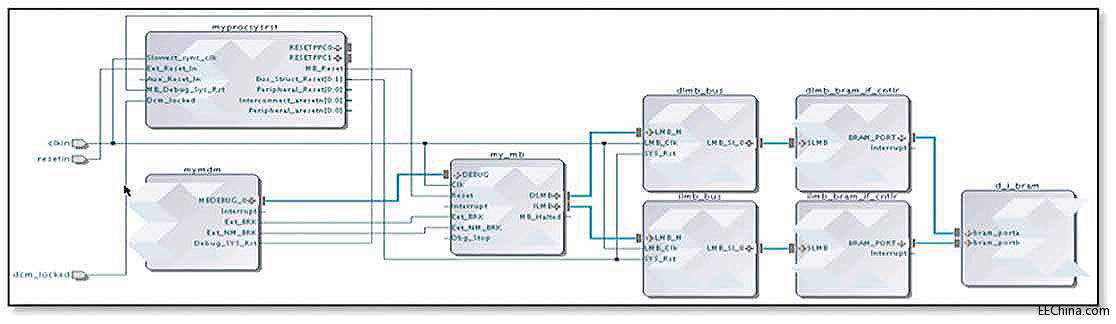

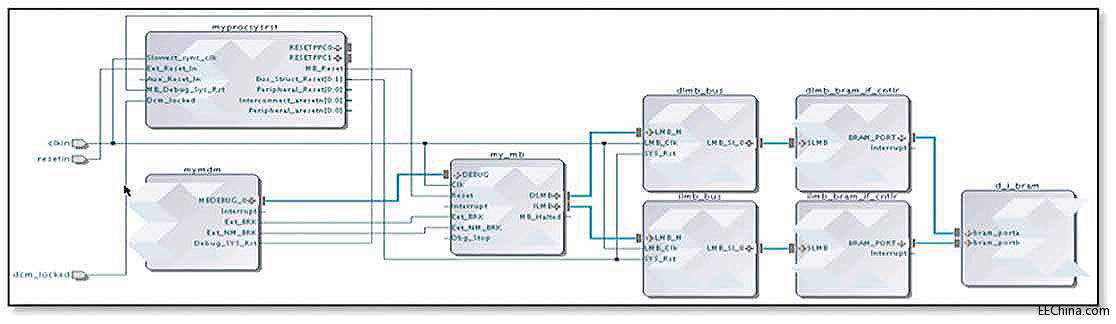

Vivado IP Integrator(Vivado IPI)(图5)是以IP为中心的设计流程,可加速系统集成进度,更轻松快捷地将不同组成部分组建成系统。利用交互式图形用户界面,IPI提供IP接口的智能自动连接、一键式IP子系统生成和强大的调试功能,可帮助设计人员轻松快捷地连接其IP Catalog中的任何乃至全部IP。这种功能使得设计人员能快速组装复杂系统,包括来自多种来源的设计资源——一些免费的、一些购买的、一些内部创建的——并且能清楚掌握所有构建块都能得到正确配置。从概念到调试从未如此神速。

简而言之,UltraScale架构在许多关键方面进行了架构创新,能成功满足下一代高性能设计的严格要求。像UltraScale这样,能确保使用系统频率越来越高的宽数据总线来实现设计,是成功开展设计工作的必要组成部分。不过,随着器件尺寸和复杂度的提升,帮助设计人员不断提高生产力变得至关重要。赛灵思提供集成块和预验证IP组合,能为设计人员带来加快实现出色解决方案所需的全部工具。

图5 – 在IP Integrator中构建设计方案和连接IP块一样简单。

来源:赛灵思中国通讯54期

高度灵活的可编程性这一极具价值的功能与诸多事情一样,要想有所得就要付出代价。利用可编程资源构建的功能可能比专门针对该功能的模块尺寸更大,甚至可能速度更慢。当然,FPGA本质上明显的优势就是具有可编程性,但赛灵思FPGA实现了专门功能、集成IP的

适当平衡,能帮助用户快实现常用功能(图3)。UltraScale架构包含针对常见通信协议的集成模块。Kintex UltraScale和Virtex UltraScale器件中包含针对PCI Express、100G Ethernet和150G Interlaken的多个集成模块,且都经过全面测试和验证,能确保实现功能。

除了通信协议之外,每个I/O Bank都包含一个可编程存储器PHY,能用存储器接口生成器(MIG)工具进行配置。这充分说明了根据需要进行集成的特性。存储器PHY和一些控制逻辑可创建为可编程专用函数,但存储器接口的数字部分用器件架构构建,针对不同模式提供所有必需的定制与支持,而这则是专门电路所难以实现的。

在器件架构中有大量其它模块,专门设计用于执行特定功能,同时保持可编程性。设计人员能以不同深度和广度来配置这些模块存储器,以级联成更大型的低功耗阵列。DSP Slice具有许多模式,能让用户根据所选功能访问模块的不同组件。因此除了门和寄存器之外,UltraScale架构上能实现大量丰富的功能。

可定制、可重复的IP能提高生产力

每个设计都包含许多不同架构构建块,相互连接构成系统。行业内有些功能已经非常完备了,从经济性角度讲完全可以将它们做成专用的固定功能模块。然而,最佳设计方法是采用可编程逻辑构建功能,并经过验证,随时按需重用。这种IP概念已经存在了很多代,但赛灵思近期推出了一些生产力增强特性(图4)。

图4 – Vivado工具加速复杂设计的创建和实现。

即插即用IP

2012年,赛灵思采用ARM®AMBA® AXI4接口作为即插即用IP的标准接口。采用统一的标准接口相比过去能大幅简化IP集成,将多种不同接口整合到一个,设计人员也不必去掌握多种不同的接口。UltraScale架构继续受益于AXI4互联的灵活性和可扩展性,从而帮助设计人员实现最快的产品上市进程,同时采用AXI4-Lite和AXI4-Stream等不同AXI4互联协议优化IP性能、面积和功耗。

Vivado IP Packager和IP Catalog采用IP-XACT标准(该标准最初由SPIRIT联盟作为工具流程中封装、集成和重用IP的标准结构推出)。IP-XACT现已获得IEEE的批准(IEEE1685-2009)。Vivado IP Packager采用在本地或共享驱动器上可扩展IP Catalog中提供的约束、测试平台和文档来创建设计。采用Vivado IP Catalog,用户能够将自己的IP、赛灵思的IP以及第三方IP无缝集成在一起,从而确保设计团队轻松一致地分享所有IP。

VIVADO IP INTEGRATOR

Vivado IP Integrator(Vivado IPI)(图5)是以IP为中心的设计流程,可加速系统集成进度,更轻松快捷地将不同组成部分组建成系统。利用交互式图形用户界面,IPI提供IP接口的智能自动连接、一键式IP子系统生成和强大的调试功能,可帮助设计人员轻松快捷地连接其IP Catalog中的任何乃至全部IP。这种功能使得设计人员能快速组装复杂系统,包括来自多种来源的设计资源——一些免费的、一些购买的、一些内部创建的——并且能清楚掌握所有构建块都能得到正确配置。从概念到调试从未如此神速。

简而言之,UltraScale架构在许多关键方面进行了架构创新,能成功满足下一代高性能设计的严格要求。像UltraScale这样,能确保使用系统频率越来越高的宽数据总线来实现设计,是成功开展设计工作的必要组成部分。不过,随着器件尺寸和复杂度的提升,帮助设计人员不断提高生产力变得至关重要。赛灵思提供集成块和预验证IP组合,能为设计人员带来加快实现出色解决方案所需的全部工具。

图5 – 在IP Integrator中构建设计方案和连接IP块一样简单。

来源:赛灵思中国通讯54期

赛灵思 DSP 总线 FPGA 收发器 电压 电路 ARM 相关文章:

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA可帮助搜索引擎降低功耗和碳排放(09-12)

- 基于Spartan-3A DSP的安全视频分析(05-01)

- 赛灵思新版视频入门套件加快视频开发速度(05-29)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 赛灵思详解新近推出的FPGA领域设计平台(12-16)