NANO2开发板实例之__FPGA实现UDP数据收发数据

NANO2开发板实例之__FPGA实现UDP数据收发数据

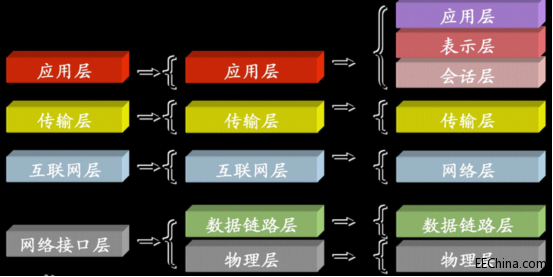

1、首先需要了解网络分层结构,直接看图,分层架构已经很清晰了。

了解一下这些名词

UDP(User Datagram Protocol)用户数据包协议

IP(Internet Protocol(网络之间互连的协议))

MAC(MediaAccessControl,媒体访问控制,数据链路层)

PHY(Physical Layer Device物理层)

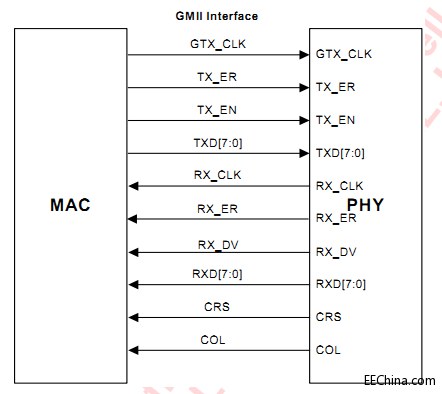

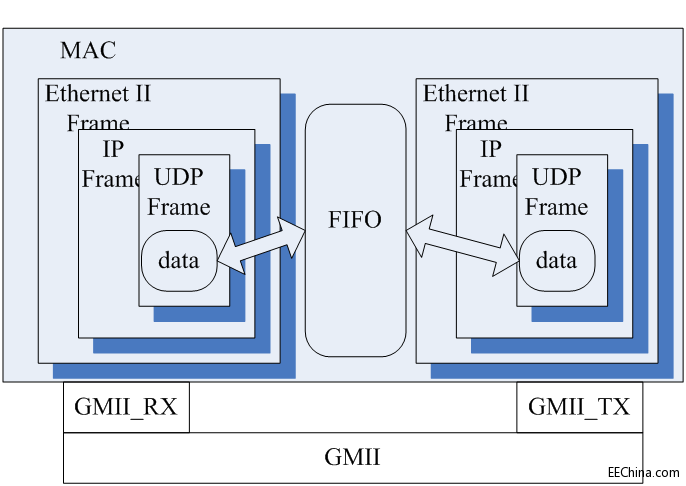

1、需要了解MAC层和PHY的硬件接口,只介绍GMII,和MII,其它类似

网络接口GMII/MII

MAC(MediaAccessControl )层和PHY层链接接口GMII (Gigabit Medium Independent Interface)

时钟接口

GTX_CLK 125M

RX_CLK 125M

数据接口

TXD[7:0] RXD[7:0]

TX_EN, 发送数据使能

TX_ER,发送数据错误

RX_DV, 接收数据有效

RX_ER 接收出错指示

MDIO/MDC 控制接口

MDC为控制时钟

MDIO控制数据

2、MII(Media Independent Interface)接口

时钟接口

TX_CLK RX_CLK 25M(100M)

数据接口

TXD[3:0]

TX_EN

TX_ER

RXD[3:0]

RX_DV

RX_ER

控制接口 MDC/MDIO

CRS 载波侦测

COL 冲突检测

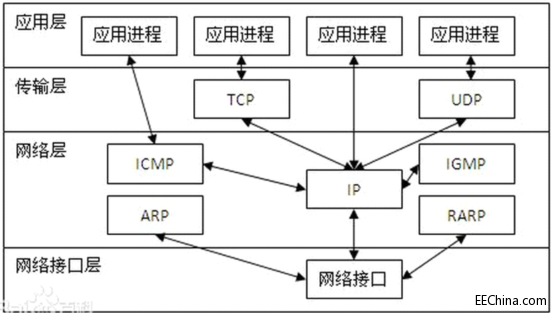

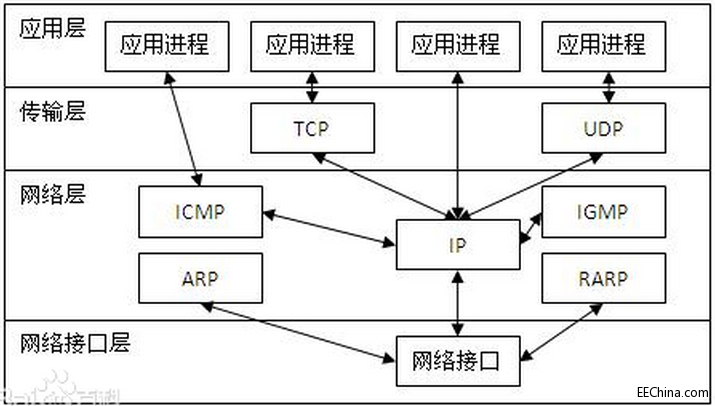

3、需要了解TCP/IP协议,UDP协议,ICMP协议

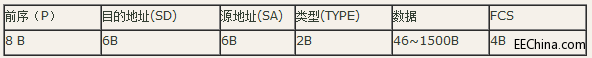

以太网帧

前序,以太网帧头,0x55*7,0xd5共8byte.

目的MAC地址,源地址MAC分别为6个byte.

协议类型,比如0x0800,表示IP协议帧,0x0806表示ARP帧。

FCS为4byte校验序列。

网络长度为以太网(Ethernet)数据帧的长度必须在46-1500字节之间,这是由以太网的物理特性决定的.

IP报文如下

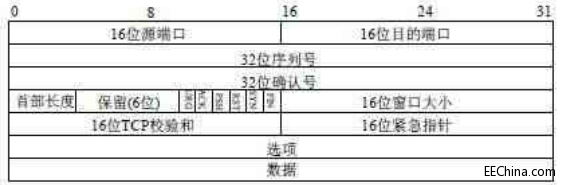

1、4位版本,表示IPV4。

2、包头长度4,为4*5=20字节,表示IP帧头有20字节。

3、16位总长度,字段为16进制表示,报文总长度,不含最后帧的FCS校验。

4、8位生存时间,表示数据包在网络上生存多久,每通过一个路由器该值减一,为0时将被路由器丢弃。TTL<64 128< TTL<256表示LINUX操作系统,64<TTL<128表示WINDOWS系统。

5、8位协议,16进制表示,常用的协议及其十进制数值包括ICMP(1)、TCP(6)、UDP(17)。

6、16位首部校验和,对IP包头的4*5包头进行校验。为了计算一份数据报的IP检验和,首先把检验和字段置为0。然后,对首部中每个16位进行二进制反码求和。

7、32为源IP,目的IP,十六进制表示。

8、选项和数据表示IP层之上的数据包。

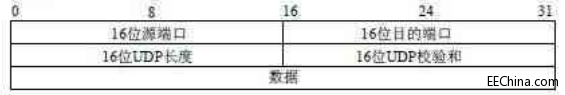

UDP报文

1、16位UDP长度,表示整个UDP包字节数。

2、16为校验和,伪头部( 4byte源IP地址 + 4byte目的IP地址 + 0x00 + 1byte协议 + UDP长度(2byte)4byte源IP地址 + 4byte目的IP地址 + 0x00 + 1byte协议(0x11)+ UDP长度(2byte))和整个报文的校验。UDP数据报文的长度可以为奇数字节,所以在计算校验和时需要在最后增加填充字节0,(填充字节只是为了计算校验和,可以不被传送)。计算方法,将校验和先置0,然后对整个字段反码求和。当然UDP报文检验字段也可以为0,在UDP传输协议中,校验和是可选的,当校验和字段为0时,表明该UDP报文未使用校验和,接收方就不需要校验和检查了,《tcp详解,卷1》书上有一句话:“如果校验和的计算结果为0,则存入的值为全1(65535),这在二进制反码计算中是等效的”。

3、数据字节数最大为1472字节,最小为**字节;最好为最好不要超过512个字节。

TCP报文

ICMP报文

1、类型字段,比如Ping请求,0x08,Ping相应0x00.

2、代码段,网络不可到达(Code=0)、主机不可到达(Code=1)、协议不可到达(Code=2)

3、检验和,对整个ICMP报文进行校验。

4、32bit ,BE,LE identifier,sequence number。IMCP包头为8字节;

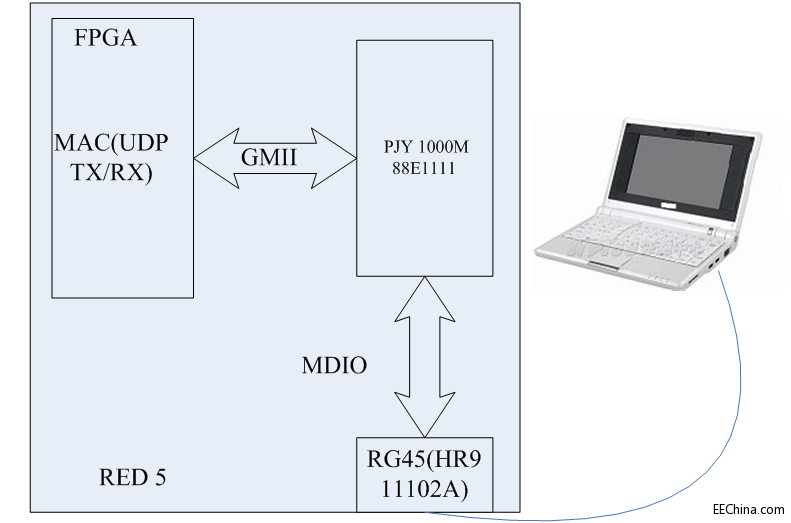

4、FPGA系统结构

5、PHY芯片

PHY 88E1111 GMII

88E1116R RGMII

RTL8201 MII

LAT971A MII

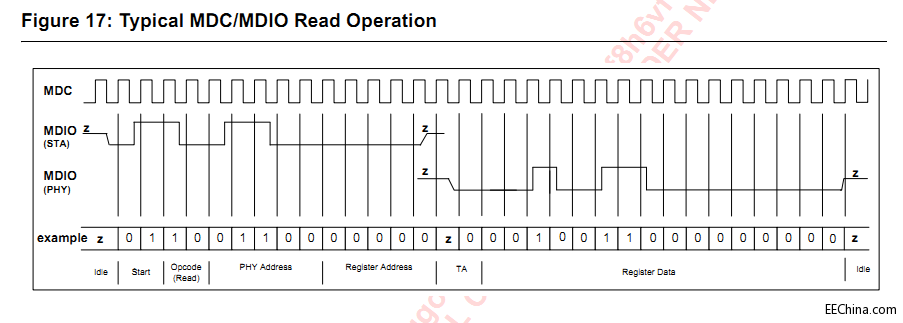

MDIO/MDC时序(读模式)

6、软件工具

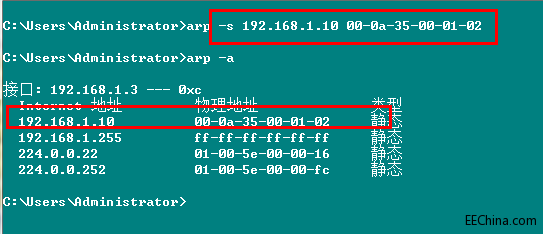

设置PC,基于网路的数据,必须包含MAC地址和IP地址,对于点对点的通信,必须设置IP,MAC地址的对应。

Wireshark抓数,对于正确的以太网数据包,可以查看到网络包的数据格式,包括mac数据,IP数据,

FPGA 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)