FPGA 101:如何在Zynq SoC上使用中断

时间:07-09

来源:互联网

点击:

-

专有定时器举例

Zynq SoC拥有许多可用的定时器和看门狗监视器。它们既可作为一个CPU的专用资源也可作为两个CPU的共享资源。如需在您的设计中高效利用这些组件,则需要中断。这些定时器和看门狗监视器包括:

- CPU 32位定时器(SCUTIMER),以CPU频率的一半计时

- CPU 32位看门狗监视器(SCUWDT),以CPU频率的一半计时

- 共享64位全局定时器(GT),以CPU频率的一半计时(每个CPU都有其自己的64位比较器;它与GT配合使用,能驱动各个CPU的专用中断)

- 系统看门狗监视时钟(WDT),可通过CPU时钟或外部来源进行计时

- 一对三重定时器计数器(TTC),每个包含三个独立定时器。在可编程逻辑中,可通过CPU时钟或来自MIO或EMIO的外部来源对TTC进行计时。

为了通过可用的定时器和看门狗监视器获得最大优势,我们需要使用Zynq SoC中断。其中配置最简单的就是专有定时器。和Zynq SoC的大多数外设一样,该定时器带有很多预定义的函数和宏指令,能帮助您高效使用这一资源。这些函数和宏指令位于:

这个文件中的函数(宏指令)能够提供许多功能,包括初始化和自测试等。此外,文件中的函数还能启动和停止定时器并对其进行管理(重启;检查是否过期;加载定时器;使能/禁用自动加载)。它们的另一项工作就是设置、使能、禁用、清除和管理定时器中断。最后,这些函数还能获取并设置预分频器。

定时器本身通过以下四个寄存器来控制:

- 专用定时器加载寄存器 – 可将该寄存器用于自动重新加载模式,包含在使能自动重新加载时被重新加载到专用定时器计数器寄存器中的数值。

- 专用定时计数寄存器 (Private Timer Counter Register) – 这是真实计数器本身。使能后,一旦寄存器达到零,则会设置中断事件标志。

- 专用定时器控制寄存器 – 控制寄存器可使能或禁用定时器、自动重新加载模式以及中断生成,还包含定时器的预分频器。

- 专用定时器中断状态寄存器 – 该寄存器包含专用定时器中断状态事件标志。

就使用GPIO而言,设置定时器所需的定时器设备ID和定时器中断ID都包含在XParameters.h文件中。在本例中,我们将使用先前开发的按钮中断。当按下按钮时,定时器将加载并开始运行(采用非自动重新加载模式)。一旦定时器过期,将生成能通过STDOUT输出一条消息的中断。然后清除该中断,以便等待下一次按下按钮。在本例中,将始终向计数器加载相同的数值;因此,在文件顶部的公告中公布了定时器计数值,如下所示:

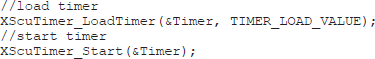

下一步是配置和初始化专用定时器并在其中加载定时器计数值。

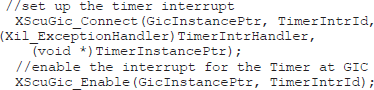

此外,我们还需要更新中断设置子例程,从而将定时器中断连接至GIC并使能定时器中断。

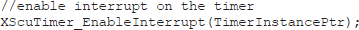

发生中断时,需要调用TimerIntrHandler函数,这时必须在GIC上以及定时器本身使能定时器中断。

定时器中断服务例程非常简单。它仅需清除挂起的中断,并通过STDOUT输出一条消息,如下所示:

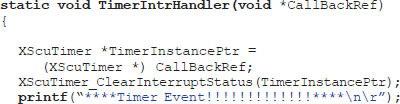

完成该操作后,最后还要修改GPIO中断服务例程,从而在每次按下按钮后启动定时器,如下所示:

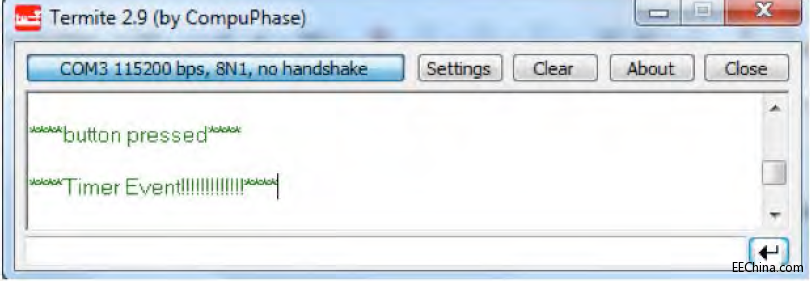

首先,我们要将定时器值加载到定时器中,然后调用定时器启动函数。现在,我们能够再次清除按钮中断并恢复处理,如图3所示。

在开始着手设计中断驱动系统时,很多工程师都会心生畏惧。但是,Zynq SoC架构以及通用中断控制器(与配备SDK的驱动器相结合)可帮助您快速、高效地启动和运行中断驱动系统。

图3 – GPIO与定时器中断事件输出的界面示例。

-

SoC 嵌入式 电子 看门狗 赛灵思 传感器 ARM Cortex FPGA LED 比较器 相关文章:

- 基于Spartan-3A DSP的安全视频分析(05-01)

- 基于Actel FPGA的PWM IP的应用(09-17)

- FPGA中的处理器IP概述(04-14)

- 用于测试SDRAM控制器的PDMA(07-01)

- 设计工具是FPGA在SoC设计中继续应用的关键(07-19)

- 基于FPGA的软件验证推动ASIC与SoC原型设计技术的发展(07-22)