基于Altera cyclone V SOC的JPEG编码分析

时间:12-26

来源:互联网

点击:

作者:ZTE中兴多媒体业务设计开发部 朱兆俊

H.264等视频压缩算法在视频会议中是核心的视频处理算法,它要求在规定的短时间内,编解码大量的视频数据,目前主要都是在DSP上运行。未来在添加4k*2k、H.265编解码等功能,并要求控制一定成本的情况下,面临DSP性能瓶颈的问题,所以希望部分算法可以下放到FPGA来实现,借助FPGA并行处理的优势,来加速整个系统。

基于altera cyclone V soc平台的试验可行性分析

1.JPEG图像压缩算法与H.264等视频压缩算法,有一定的相似性,并要简单很多,有一定的借鉴意义,故本次短期试验使用JPEG算法来验证该SOC平台;

2.JPEG压缩算法如果完全在FPGA上用VerilogHDL语言实现,有一定难度,并且开发周期很长,而C语言源码,已经比较成熟,移植到ARM比较简单;

3.经考察,altera cyclone V soc平台,拥有两颗速度高达800Mhz的cortex A9内核,并有大容量的逻辑单元,和高速收发模块。FPGA与ARM之间的AXI标准总线,速度更是高达100Gbit,对传输高清视频数据,即使4K*2K也是绰绰有余。

试验过程

JPEG是Joint Photographic Experts Group的缩写,即ISO和IEC联合图像专家组,负责静态图像压缩标准的制定,这个专家组开发的算法就被称为JPEG算法,并且已经成为了大家通用的标准,即JPEG标准。JPEG压缩是有损压缩,但这个损失的部分是人的视觉不容易察觉到的部分,它充分利用了人眼对计算机色彩中的高频信息部分不敏感的特点,来大大节省了需要处理的数据信息。

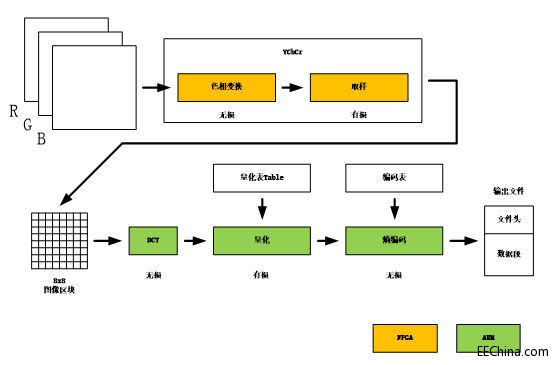

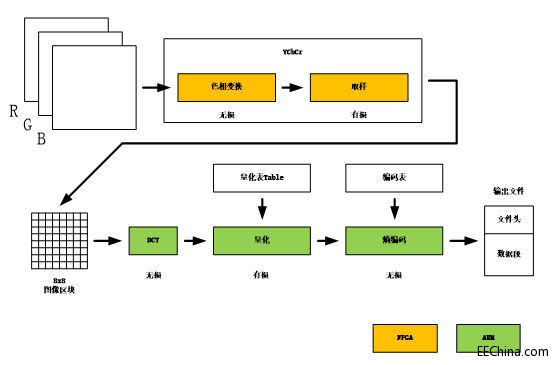

JPEG编码中主要涉及到的内容主要包括:

1. Color Model Conversion(色彩模型)

2. DCT(Discrete Cosine Transform离散余弦变换

3. 重排列DCT结果

4. 量化

5. RLE编码

6. 范式Huffman编码

7. DC的编码

本次试验ARM侧运行LINUX操作系统,并将Color Model Conversion部分,下发给FPGA侧来实现,如上图,黄色区域标记。其中ARM核与FPGA的数据交互运用了HPS-to-FPGA x64 Bridge,该总线的读写操作都是在MMAP(将底层地址空间映射到用户层)后,通过使用HWlib库函数来实现。在FPGA侧,运用Qsys工具,添加Application_logic用户逻辑模块,来实现Color Model Conversion功能,如下图黄色区域标记。

试验结果

1. 整个编码过程正常,以下左侧为编码前的真彩.bmp格式图片,右侧为编码后的.jpg格式图片。

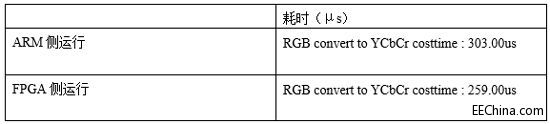

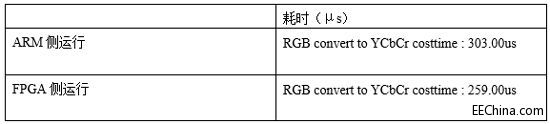

2. 通过调用LINUX操作系统时钟函数gettimeofday(&tv,&tz)的方式,统计Color Model Conversion部分在ARM侧运行,和在FPGA侧运行消耗的时间:

从表中可以看出,FPGA在大数据量的处理时,能发挥并行的优势,使运算速度得到提升。因试验开发程度有限,所以速度提升不是很明显。相信在将更多数据处理任务交给FPGA完成后,能获得更高的系统性能。

试验结论

1. cycloneV SOC有ARM核的存在,可以运用成熟的C语言代码,缩短开发时间;

2. cycloneV SOC有大量逻辑单元,可以协助处理大量数据,提高系统性能;

3. cycloneV SOC成本低廉,满足成本控制要求;

H.264等视频压缩算法在视频会议中是核心的视频处理算法,它要求在规定的短时间内,编解码大量的视频数据,目前主要都是在DSP上运行。未来在添加4k*2k、H.265编解码等功能,并要求控制一定成本的情况下,面临DSP性能瓶颈的问题,所以希望部分算法可以下放到FPGA来实现,借助FPGA并行处理的优势,来加速整个系统。

基于altera cyclone V soc平台的试验可行性分析

1.JPEG图像压缩算法与H.264等视频压缩算法,有一定的相似性,并要简单很多,有一定的借鉴意义,故本次短期试验使用JPEG算法来验证该SOC平台;

2.JPEG压缩算法如果完全在FPGA上用VerilogHDL语言实现,有一定难度,并且开发周期很长,而C语言源码,已经比较成熟,移植到ARM比较简单;

3.经考察,altera cyclone V soc平台,拥有两颗速度高达800Mhz的cortex A9内核,并有大容量的逻辑单元,和高速收发模块。FPGA与ARM之间的AXI标准总线,速度更是高达100Gbit,对传输高清视频数据,即使4K*2K也是绰绰有余。

试验过程

JPEG是Joint Photographic Experts Group的缩写,即ISO和IEC联合图像专家组,负责静态图像压缩标准的制定,这个专家组开发的算法就被称为JPEG算法,并且已经成为了大家通用的标准,即JPEG标准。JPEG压缩是有损压缩,但这个损失的部分是人的视觉不容易察觉到的部分,它充分利用了人眼对计算机色彩中的高频信息部分不敏感的特点,来大大节省了需要处理的数据信息。

JPEG编码中主要涉及到的内容主要包括:

1. Color Model Conversion(色彩模型)

2. DCT(Discrete Cosine Transform离散余弦变换

3. 重排列DCT结果

4. 量化

5. RLE编码

6. 范式Huffman编码

7. DC的编码

本次试验ARM侧运行LINUX操作系统,并将Color Model Conversion部分,下发给FPGA侧来实现,如上图,黄色区域标记。其中ARM核与FPGA的数据交互运用了HPS-to-FPGA x64 Bridge,该总线的读写操作都是在MMAP(将底层地址空间映射到用户层)后,通过使用HWlib库函数来实现。在FPGA侧,运用Qsys工具,添加Application_logic用户逻辑模块,来实现Color Model Conversion功能,如下图黄色区域标记。

试验结果

1. 整个编码过程正常,以下左侧为编码前的真彩.bmp格式图片,右侧为编码后的.jpg格式图片。

2. 通过调用LINUX操作系统时钟函数gettimeofday(&tv,&tz)的方式,统计Color Model Conversion部分在ARM侧运行,和在FPGA侧运行消耗的时间:

从表中可以看出,FPGA在大数据量的处理时,能发挥并行的优势,使运算速度得到提升。因试验开发程度有限,所以速度提升不是很明显。相信在将更多数据处理任务交给FPGA完成后,能获得更高的系统性能。

试验结论

1. cycloneV SOC有ARM核的存在,可以运用成熟的C语言代码,缩短开发时间;

2. cycloneV SOC有大量逻辑单元,可以协助处理大量数据,提高系统性能;

3. cycloneV SOC成本低廉,满足成本控制要求;

DSP FPGA Verilog C语言 ARM 总线 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- FPGA作为协处理器在实时系统中的应用(04-08)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)

- 基于Spartan-3A DSP的安全视频分析(05-01)