MicroBlaze如何与Zynq SoC和平共存

时间:08-21

来源:互联网

点击:

作者:Bill Kafig, Praveen Venugopal, 赛灵思公司

赛灵思 Zynq-7000 All Programmable SoC已具有很强的板载处理能力。但是Zynq应用处理单元(APU)中强大的双Cortex-A9处理器和相关外设的存在并不妨碍您在同一封装中添加一个或多个MicroBlaze?处理器,只要能让应用受益就好。

为什么要给处理功能已经很强大的解决方案添加MicroBlaze呢?首先就是可靠性的问题。单线程会大幅提高可靠性。您可以针对计算密集型任务为每个Cortex-A9都布置一个线程,而且能根据需要为其它线程实例化任何数量的MicroBlaze处理器。其次,您可将任何杂务交给MicroBlaze去完成,让处理功能强大的Cortex-A9去执行最需要它的工作,充分发挥其用武之地,从而节省数个关键的工作周期。

下面这个例子能反映以上两种情况。设想一下,一个任务需要长期高强度计算,同时还要监控用户输入。这里,MicroBlaze可管理用户输入(频率较低、计算强度不高),并写入APU存储器空间,这样APU闲置时(也就是完成了处理任务时)就能看看接下来需要处理什么信息。

一旦您决定在基于Zynq的设计中添加一个MicroBlaze处理器,马上就会发现一些问题。首要问题就是APU如何与MicroBlaze通信,哪些处理器系统(PS)资源可供MicroBlaze使用。包括ZC702和Zedboard等在内的许多开发板将许多外设直接映射到与处理系统相连的引脚。可编程逻辑(PL)中,这些引脚不能直接访问MicroBlaze。处理系统还包含多种不同定时器和中断资源。有什么办法能从MicroBlaze领域访问这些资源吗?

PS与PL之间的接口

处理器系统和可编程逻辑紧密结合,这意味着Cortex-A9、窥探控制单元(SCU)、PS外设、时钟管理及其它功能与可编程逻辑之间存在多个紧密的集成连接。事实上,PS和PL之间共有6种不同类型的互联,您可将这些互联类型彼此结合使用。此外,许多路径是对称的,也就是说PC能启动到PL的连接,而PL也能启动到PS的连接。

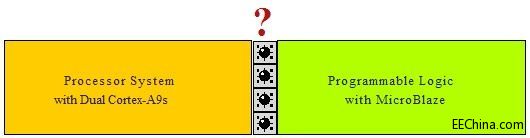

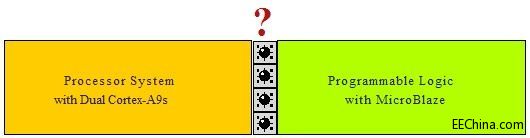

图1:PL中PS和MicroBlaze的边界是一片雷区吗?二者能否共享资源?

赛灵思公司目前提供的应用指南、用户指南和白皮书等大量资料均介绍了作为设计“核心”的Zynq-7000 APU如何利用可编程逻辑来访问存储器、基于PL的外设和硬芯片外设(如PCIe模块、BRAM、DSP48和千兆位级收发器等)。要分析MicroBlaze如何成为其自身领域的主导,逻辑上的第一步就是看看6个接口变量,首先从通用、高性能和加速器一致性端口这三类AXI接口入手。

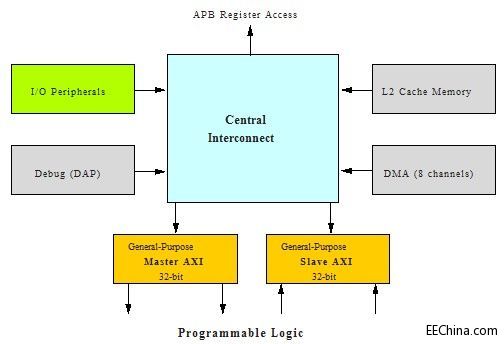

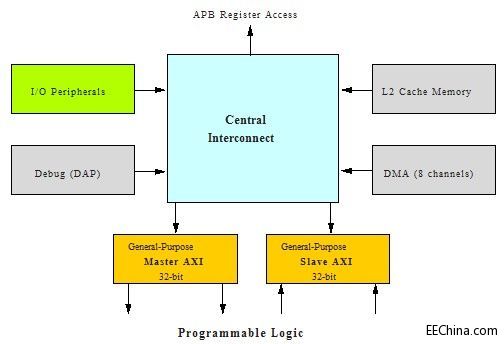

PS有两个连接到PL的主AXI通道和两个由PL启动的从通道(图2)。这里的“主”是指AXI通道为发起方,能启动数据交换,而“从”在只能用于响应到达的数据。主AXI通道通常用来与PL中的外设通信。从AXI通道负责响应PL的请求,其中可能包括MicroBlaze处理器所执行的事务处理。这些AXI通道连接到PS的中央互联,可路由到许多资源。

此外,还有4个高性能(64位宽)AXI通道连接点。从PS角度来说,所有这4个通道均为从通道,连接至PS中的存储器接口子系统(图3)。这4个通道的目的就是让PS中的主设备启动DDR存储器事务处理。

这种存储器互联和DDR存储器控制器是所有资源到DDR存储器的门户。虽然Cortex-A9处理器的优先级通常高于从AXI连接,但4个AXI连接中每个都有一个“现在为我服务”信号,能让发出该请求的通道获得优先级。未断言该信号时,架构、采用循环机制确定哪个请求方有权访问特定类型存储器。

加速器一致性端口(ACP)是另一种PL的32位AXI PS从连接。ACP的独特之处在于它直接连接到SCU中。SCU的任务就是确保L1、L2和DDR存储器之间的一致性。采用ACP,您能访问PS中的每个Cortex- A9处理器的高速缓存存储器,而不必担心与主存储器中的数据同步问题(硬件会自动处理好这个问题)。该功能不仅可大幅降低设计负担,而且还能显著加速处理器与PL之间的数据传输。

图2:到处理系统中央互联的简化连接。

图3:到DDR存储器控制器和片上存储器(OCM)的简化连接。

除了AXI链接之外,可扩展多路输入输出(EMIO)信号也可用于路由许多PS的硬外设直至PL,以便访问封装引脚。只有54个封装引脚直接连接到PS,不过PS的硬外设可使用的引脚数量大大超过54个。EMIO是PS硬外设和PL之间的通道。这些I/O信号可直接路由到PL可用的封装引脚,而您也可利用这些引脚与PL中兼容的外设进行通信。

PS和PL之间另外的各种杂项信号可以分为5个基本类:时钟与复位、中断信号、事件信号、空闲AXI与DDR存储器信号,以及DMA信号。

* 时钟与复位:PS为PL提供4个独立的可编程频率。通常这些时钟之一用于AXI连接。每个时钟域都有自己的域复位信号,可重设与该域关联的任何器件。

* 中断信号:PS中的通用中断控制器(GIC)负责收集所有可用源的中断,包括PS外设的所有中断源和可编程逻辑的16个“外设”类型中断。此外,还有4个连接到CPU(IRQ0、 IRQ1、FIQ0和FIQ1)的直接中断。来自PS外设的共28个中断可提供给PL。

* 事件信号:这些“带外”异步信号说明PS的特殊情况。PS提供一系列信号用于表明哪个CPU进入待机模式,哪个CPU执行了SEV(“发送事件”)指令。PS可用事件信号从WFE(“等待事件”)状态中唤醒。

* 空闲AXI与DDR存储器信号:PS的空闲AXI信号用来指示PL中没有未处理的AXI事务处理。该信号由PL驱动,是用来启动PS总线时钟关断功能的条件之一,确保所有PL总线器件均处于闲置状态。DDR紧急/仲裁信号用来向PS DDR存储器控制器的4个AXI端口DDR仲裁表示关键的存储器处于紧张状况。

* DMA信号:PS的直接存储器访问(DMA)模块通过一系列“请求和确认”信号与PL从设备通信。

图4:硬件设计实例方框图。

赛灵思 Zynq-7000 All Programmable SoC已具有很强的板载处理能力。但是Zynq应用处理单元(APU)中强大的双Cortex-A9处理器和相关外设的存在并不妨碍您在同一封装中添加一个或多个MicroBlaze?处理器,只要能让应用受益就好。

为什么要给处理功能已经很强大的解决方案添加MicroBlaze呢?首先就是可靠性的问题。单线程会大幅提高可靠性。您可以针对计算密集型任务为每个Cortex-A9都布置一个线程,而且能根据需要为其它线程实例化任何数量的MicroBlaze处理器。其次,您可将任何杂务交给MicroBlaze去完成,让处理功能强大的Cortex-A9去执行最需要它的工作,充分发挥其用武之地,从而节省数个关键的工作周期。

下面这个例子能反映以上两种情况。设想一下,一个任务需要长期高强度计算,同时还要监控用户输入。这里,MicroBlaze可管理用户输入(频率较低、计算强度不高),并写入APU存储器空间,这样APU闲置时(也就是完成了处理任务时)就能看看接下来需要处理什么信息。

一旦您决定在基于Zynq的设计中添加一个MicroBlaze处理器,马上就会发现一些问题。首要问题就是APU如何与MicroBlaze通信,哪些处理器系统(PS)资源可供MicroBlaze使用。包括ZC702和Zedboard等在内的许多开发板将许多外设直接映射到与处理系统相连的引脚。可编程逻辑(PL)中,这些引脚不能直接访问MicroBlaze。处理系统还包含多种不同定时器和中断资源。有什么办法能从MicroBlaze领域访问这些资源吗?

PS与PL之间的接口

处理器系统和可编程逻辑紧密结合,这意味着Cortex-A9、窥探控制单元(SCU)、PS外设、时钟管理及其它功能与可编程逻辑之间存在多个紧密的集成连接。事实上,PS和PL之间共有6种不同类型的互联,您可将这些互联类型彼此结合使用。此外,许多路径是对称的,也就是说PC能启动到PL的连接,而PL也能启动到PS的连接。

图1:PL中PS和MicroBlaze的边界是一片雷区吗?二者能否共享资源?

赛灵思公司目前提供的应用指南、用户指南和白皮书等大量资料均介绍了作为设计“核心”的Zynq-7000 APU如何利用可编程逻辑来访问存储器、基于PL的外设和硬芯片外设(如PCIe模块、BRAM、DSP48和千兆位级收发器等)。要分析MicroBlaze如何成为其自身领域的主导,逻辑上的第一步就是看看6个接口变量,首先从通用、高性能和加速器一致性端口这三类AXI接口入手。

PS有两个连接到PL的主AXI通道和两个由PL启动的从通道(图2)。这里的“主”是指AXI通道为发起方,能启动数据交换,而“从”在只能用于响应到达的数据。主AXI通道通常用来与PL中的外设通信。从AXI通道负责响应PL的请求,其中可能包括MicroBlaze处理器所执行的事务处理。这些AXI通道连接到PS的中央互联,可路由到许多资源。

此外,还有4个高性能(64位宽)AXI通道连接点。从PS角度来说,所有这4个通道均为从通道,连接至PS中的存储器接口子系统(图3)。这4个通道的目的就是让PS中的主设备启动DDR存储器事务处理。

这种存储器互联和DDR存储器控制器是所有资源到DDR存储器的门户。虽然Cortex-A9处理器的优先级通常高于从AXI连接,但4个AXI连接中每个都有一个“现在为我服务”信号,能让发出该请求的通道获得优先级。未断言该信号时,架构、采用循环机制确定哪个请求方有权访问特定类型存储器。

加速器一致性端口(ACP)是另一种PL的32位AXI PS从连接。ACP的独特之处在于它直接连接到SCU中。SCU的任务就是确保L1、L2和DDR存储器之间的一致性。采用ACP,您能访问PS中的每个Cortex- A9处理器的高速缓存存储器,而不必担心与主存储器中的数据同步问题(硬件会自动处理好这个问题)。该功能不仅可大幅降低设计负担,而且还能显著加速处理器与PL之间的数据传输。

图2:到处理系统中央互联的简化连接。

图3:到DDR存储器控制器和片上存储器(OCM)的简化连接。

除了AXI链接之外,可扩展多路输入输出(EMIO)信号也可用于路由许多PS的硬外设直至PL,以便访问封装引脚。只有54个封装引脚直接连接到PS,不过PS的硬外设可使用的引脚数量大大超过54个。EMIO是PS硬外设和PL之间的通道。这些I/O信号可直接路由到PL可用的封装引脚,而您也可利用这些引脚与PL中兼容的外设进行通信。

PS和PL之间另外的各种杂项信号可以分为5个基本类:时钟与复位、中断信号、事件信号、空闲AXI与DDR存储器信号,以及DMA信号。

* 时钟与复位:PS为PL提供4个独立的可编程频率。通常这些时钟之一用于AXI连接。每个时钟域都有自己的域复位信号,可重设与该域关联的任何器件。

* 中断信号:PS中的通用中断控制器(GIC)负责收集所有可用源的中断,包括PS外设的所有中断源和可编程逻辑的16个“外设”类型中断。此外,还有4个连接到CPU(IRQ0、 IRQ1、FIQ0和FIQ1)的直接中断。来自PS外设的共28个中断可提供给PL。

* 事件信号:这些“带外”异步信号说明PS的特殊情况。PS提供一系列信号用于表明哪个CPU进入待机模式,哪个CPU执行了SEV(“发送事件”)指令。PS可用事件信号从WFE(“等待事件”)状态中唤醒。

* 空闲AXI与DDR存储器信号:PS的空闲AXI信号用来指示PL中没有未处理的AXI事务处理。该信号由PL驱动,是用来启动PS总线时钟关断功能的条件之一,确保所有PL总线器件均处于闲置状态。DDR紧急/仲裁信号用来向PS DDR存储器控制器的4个AXI端口DDR仲裁表示关键的存储器处于紧张状况。

* DMA信号:PS的直接存储器访问(DMA)模块通过一系列“请求和确认”信号与PL从设备通信。

图4:硬件设计实例方框图。

赛灵思 SoC Cortex DSP 收发器 总线 PWM LED 嵌入式 Xilinx 相关文章:

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA可帮助搜索引擎降低功耗和碳排放(09-12)

- 基于Spartan-3A DSP的安全视频分析(05-01)

- 赛灵思新版视频入门套件加快视频开发速度(05-29)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 赛灵思详解新近推出的FPGA领域设计平台(12-16)