基于嵌入式的电缆故障检测仪设计

时间:03-25

来源:互联网

点击:

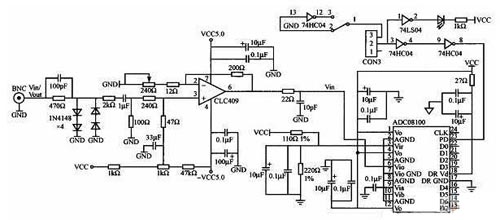

图3 A/D转换电路

3.4 时钟信号的产生

检测脉冲的产生、ADC08100的采样,以及异步FIFO的数据缓存构成了一个高速A/D数据采集系统。这对于各种信号的时间配合要求很高,需要专门的时钟单元来配合,以使电路工作在正确的时序之下。在FPGA中可方便地定制时钟模块来产生A/D采样时钟、异步存储器的读写时钟,以及脉冲发生模块的计数时钟。所有的时钟都是由一个高速的时钟来实现同步的,并且整个系统是在同一个启动信号下同步运行的,从而保证了采样的时序要求。

3.5 电源模块

系统中既有模拟电路又有高速数字电路,使用电源种类复杂,存在+5 V、+3.3 V、+1.2 V、-5 V等多种电源信号。在电路板设计制作中既要减小高频数字信号对模拟信号的电磁干扰,又要避免各种电源之间的干扰,因此需合理规划模块布局及布线走向以提高信号稳定性。

4 软件设计

软件设计主要包括FPGA的开发应用、应用程序设计以及液晶显示器的驱动程序设计等。

4.1 FPGA开发应用

现场可编程逻辑器件FPGA(Field Programming Gate Array)具有高密度、高速度、低功耗、功能强大等特点。在此系统中采用了Altera公司的CycloneII系列器件来实现高速的数据采集、存储功能,是在QuartuslI 7.1软件中使用硬件描述语言VHDL来设计完成的。高密度可编程逻辑器件的设计流程包括:设计准备、设计输入、设计处理和器件编程4个步骤,以及相应的功能仿真(前仿真)、时序仿真(后仿真)和器件测试3个设计验证过程。

本设计中,主要包括Nios微处理器、脉冲发生、高速时钟以及高速数据存储FIFO等模块的设计。

4.2 应用程序设计

应用程序控制检测任务的启动和结束、脉冲发送接收模式的选择、A/D采样数据的处理计算、故障性质和位置的判断以及结果输出等。

5.结语

本文提出了基于Nios软核的电缆故障检测仪设计方案。对于脉冲反射法检测故障的具体实现,提出了基于现场可编程逻辑器件的高速采样系统的设计思路,并在此基础上对系统进行了全面的设计。仿真和试验结果表明,该系统能够实现对电缆的断路、短路等故障的检测,具有在线监测、易于控制的优点,以及灵活和良好的扩展功能。

嵌入式 FPGA 电压 电阻 电子 电路 Altera ADC 放大器 二极管 运算放大器 电源模块 模拟电路 显示器 Quartus VHDL 仿真 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)