基于FPGA的雷达中/视频数据采集与回放系统设计

时间:03-24

来源:互联网

点击:

4 系统调试和测试

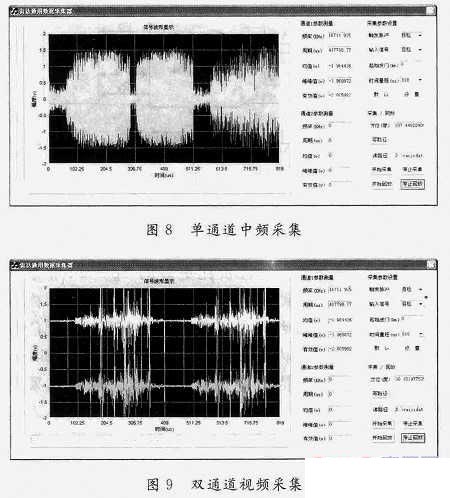

在完成了系统的硬件设计和软件设计以后,需要进行综合调试和测试。通过调试,不断优化程序代码,对程序中的问题及时更正修改,使系统的性能得以提高,工作状态更加稳定。测试的过程中可以修正电路中元器件的参数等,以免理论分析与实际状态的差距引起系统的参数不符合要求。目前,本系统可以实现对多种型号的雷达进行实际外场数据采集。图8,图9分别为本系统采集到的某部岸基对海警戒雷达(全相参脉冲压缩体制)的单路中频(未经脉冲压缩处理)和双路正交视频(经过脉冲压缩处理)回波信号。

实验表明该系统完全满足所提出的指标要求,能够做到大容量高速连续采集,而且稳定可靠,采集所得到的数据可以满足信号处理和目标识别的要求。

5 结语

研究了雷达中/视频数据采集与回放系统的总体方案,即由信号调理模块、核心采集模块、缓冲模块、传输模块和应用程序显示模块组成。FPGA与上位机间的数据交换通过USB 2.0接口实现,并运用虚拟技术,采用了Visual C++语言设计系统的计算机实时显示界面。设计中运用硬件描述语言对FPGA进行编程,在完成了对输入信号的采集和记录的同时,实现了对输入信号的防抖动、过零检测、等精度测频及电压最值、峰峰值和平均值的测量,使得该系统能对信号参数进行准确测量。该系统被封装于一个小型的屏蔽盒内,非常便于携带,可方便应用于外场雷达的数据采集。

集成电路 FPGA USB 电路 总线 电压 ADI 放大器 单片机 C语言 VHDL 虚拟仪器 相关文章:

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA 重复配置和测试的实现(08-14)

- 适用于消费性市场的nano FPGA技术(09-27)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)