基于FPGA圆阵超声自适应波束形成的设计

时间:12-06

来源:互联网

点击:

2.2.2 存储模块

存储模块采用8位和16位双口RAM(如图3所示)作为信号数据和权值数据的存入和读取存储器,分别用来存放输入信号x、权值ω和误差e,分别由控制信号clkregbt,clk_regw和clk_rege来控制信号的写入和读出。其中x_ram用来存放输入信号;w_ram存放权值,其输入为系数更新模块的输出,输出为更新后的权值。

2.2.3 自适应处理及复数乘加器模块

数字波束形成器是通过加权因子对空间不同阵元接收信号的加权求和而成的。由于加权因子相当于滤波器系数,而输入的信号为空间位置不同的阵元的接收信号。所以可将数字波束形成器等同于一个空域滤波器来实现。

3 系统仿真与验证

本文设计的核心部分是基于Stratix系列EPlS10芯片设计的分别对I/Q两路原始数据进行DLMS自适应算法和复数乘加运算,在QuartusⅡ环境下用VHDL语言编写了各功能模块,并进行了仿真,共占用了2 703个逻辑单元,同时应用Matlab对数字结果进行波形仿真,以下为仿真验证的结果。

图5为主控模块的仿真波形,其中ST0,ST1,ST2,ST3为复数乘法的4种组合,clk_regbt用来控制乘法器完成乘法,counter_bt用来控制乘数的位选,clk_reg用来控制运算新数的进入、上次计算的完毕和结果的输出。

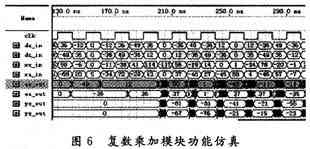

图6为复数乘加模块功能仿真结果,dc_out,ds_out,xc_out,xs_out分别是输入信号和期望信号的实部和虚部,ec_out,es_out,yc_out,ys_out分别为误差和滤波输出的实部和虚部。

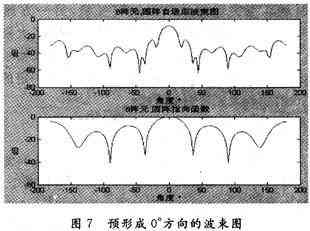

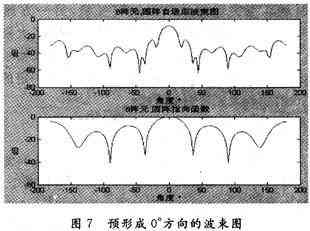

图7为系统仿真测试结果:系统预形成波束方向为0°方向,干扰从45°传来,通过仿真结果可以看出,主波束在0°方向形成,和预形成主波束吻合,在45°干扰方向形成零陷,并且提高了主波束的增益,满足系统的设计要求。

4 结 语

自适应DBF是现代声纳阵列信号处理的关键技术之一,本文介绍了利用FPGA芯片实现的自适应BDF结构,给出了相应的硬件设计和仿真验证,采用FPGA结构,硬件成本低,在自适应阵列信号处理系统中具有很好的应用前景。

存储模块采用8位和16位双口RAM(如图3所示)作为信号数据和权值数据的存入和读取存储器,分别用来存放输入信号x、权值ω和误差e,分别由控制信号clkregbt,clk_regw和clk_rege来控制信号的写入和读出。其中x_ram用来存放输入信号;w_ram存放权值,其输入为系数更新模块的输出,输出为更新后的权值。

2.2.3 自适应处理及复数乘加器模块

数字波束形成器是通过加权因子对空间不同阵元接收信号的加权求和而成的。由于加权因子相当于滤波器系数,而输入的信号为空间位置不同的阵元的接收信号。所以可将数字波束形成器等同于一个空域滤波器来实现。

3 系统仿真与验证

本文设计的核心部分是基于Stratix系列EPlS10芯片设计的分别对I/Q两路原始数据进行DLMS自适应算法和复数乘加运算,在QuartusⅡ环境下用VHDL语言编写了各功能模块,并进行了仿真,共占用了2 703个逻辑单元,同时应用Matlab对数字结果进行波形仿真,以下为仿真验证的结果。

图5为主控模块的仿真波形,其中ST0,ST1,ST2,ST3为复数乘法的4种组合,clk_regbt用来控制乘法器完成乘法,counter_bt用来控制乘数的位选,clk_reg用来控制运算新数的进入、上次计算的完毕和结果的输出。

图6为复数乘加模块功能仿真结果,dc_out,ds_out,xc_out,xs_out分别是输入信号和期望信号的实部和虚部,ec_out,es_out,yc_out,ys_out分别为误差和滤波输出的实部和虚部。

图7为系统仿真测试结果:系统预形成波束方向为0°方向,干扰从45°传来,通过仿真结果可以看出,主波束在0°方向形成,和预形成主波束吻合,在45°干扰方向形成零陷,并且提高了主波束的增益,满足系统的设计要求。

4 结 语

自适应DBF是现代声纳阵列信号处理的关键技术之一,本文介绍了利用FPGA芯片实现的自适应BDF结构,给出了相应的硬件设计和仿真验证,采用FPGA结构,硬件成本低,在自适应阵列信号处理系统中具有很好的应用前景。

DSP 电路 CPLD FPGA 滤波器 仿真 Quartus VHDL 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- FPGA作为协处理器在实时系统中的应用(04-08)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)

- 基于Spartan-3A DSP的安全视频分析(05-01)