基于DSP与FPGA的光栅地震检波器的信号处理

时间:11-29

来源:互联网

点击:

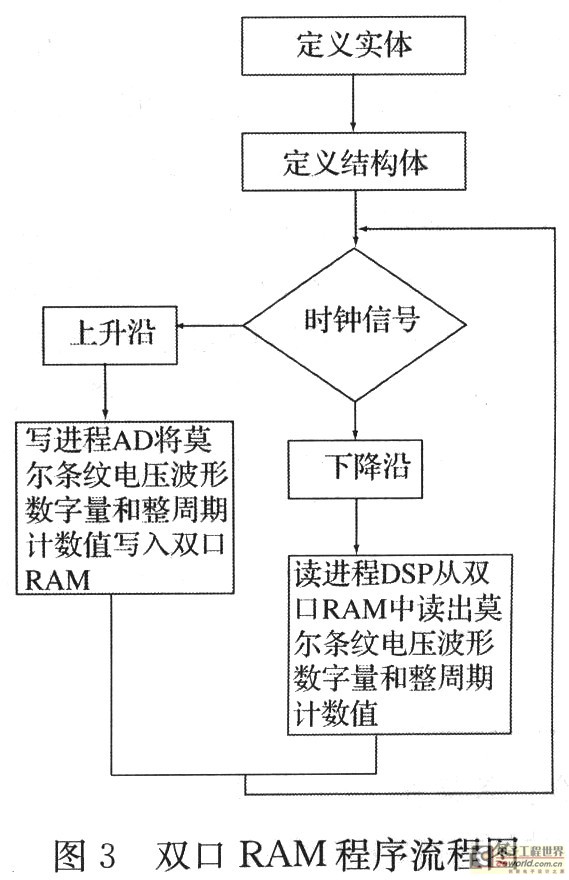

3.3 双口RAM的仿真结果

图4为该进程的仿真时序图,由图可见第一个时钟的上升沿数据输入端口data_in的值为4,这时写选通端口write_address选通地址1,然后对应着地址1的存储器模块ram_block1的内的值在此刻刷新为4,这说明写进程正确。同时应注意到读地址选通信号read_address的值被传递到读地址寄存器read_address_reg中,read_address_reg中的值被刷新为1。当第一个时钟的下降沿到来时,信号输出端口data_out根据读地址寄存器read_address_reg中的地址值1选通ram_block1,此时data_out的值刷新为4,这说明读进程也正确。

4 DSP的软件细分

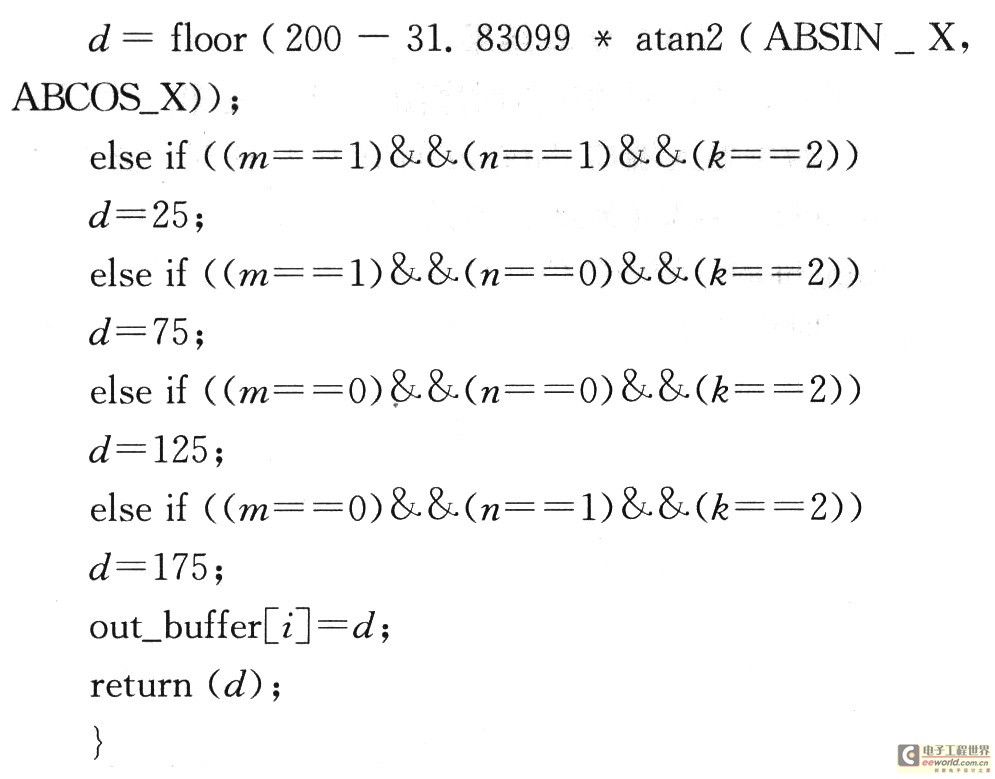

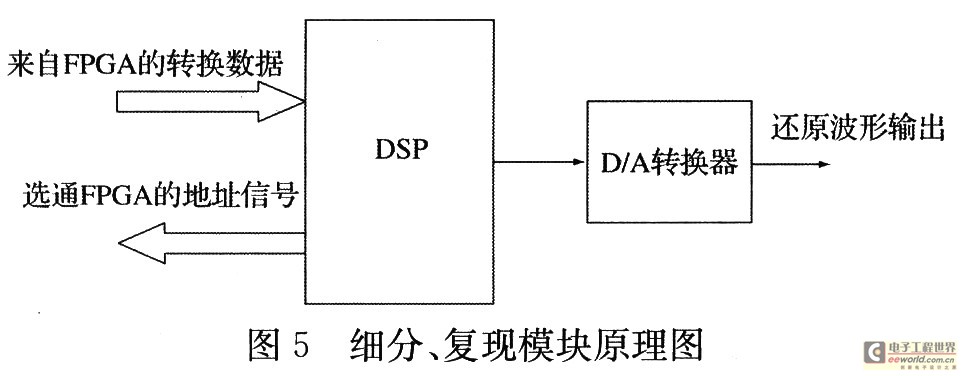

采用大数可逆计数与小数细分计数的软件细分技术。其中大数计数是对莫尔条纹整周期数进行可逆的加减计数,这部分功能有采集模块中的FPGA来完成,小数计数是对莫尔条纹不到一个周期信号细分结果进行计数,其功能由DSP来完成。运算的结果为大数计数结果乘以光栅栅距与小数计数结果乘以细分当量之和,其中细分当量为光栅栅距除以细分倍数。该模块的硬件原理图如图5所示。

通过DSP的地址选通线依次选通读取FPGA中三个数据缓存区中的数据,缓存区分别存放两路模拟信号的数字量与加减计数器的累加计数值,然后利用公式R=N*w+K*L求出任意一点谐振子的幅值并输出。式中N为整周期的累加计数值,W为光栅栅距,K为细分计数,L=W/M,M为细分倍数。该细分模块主要是完成对细分计数K值、和幅值R值的求取,并完成对幅值的数字量转换并输出。

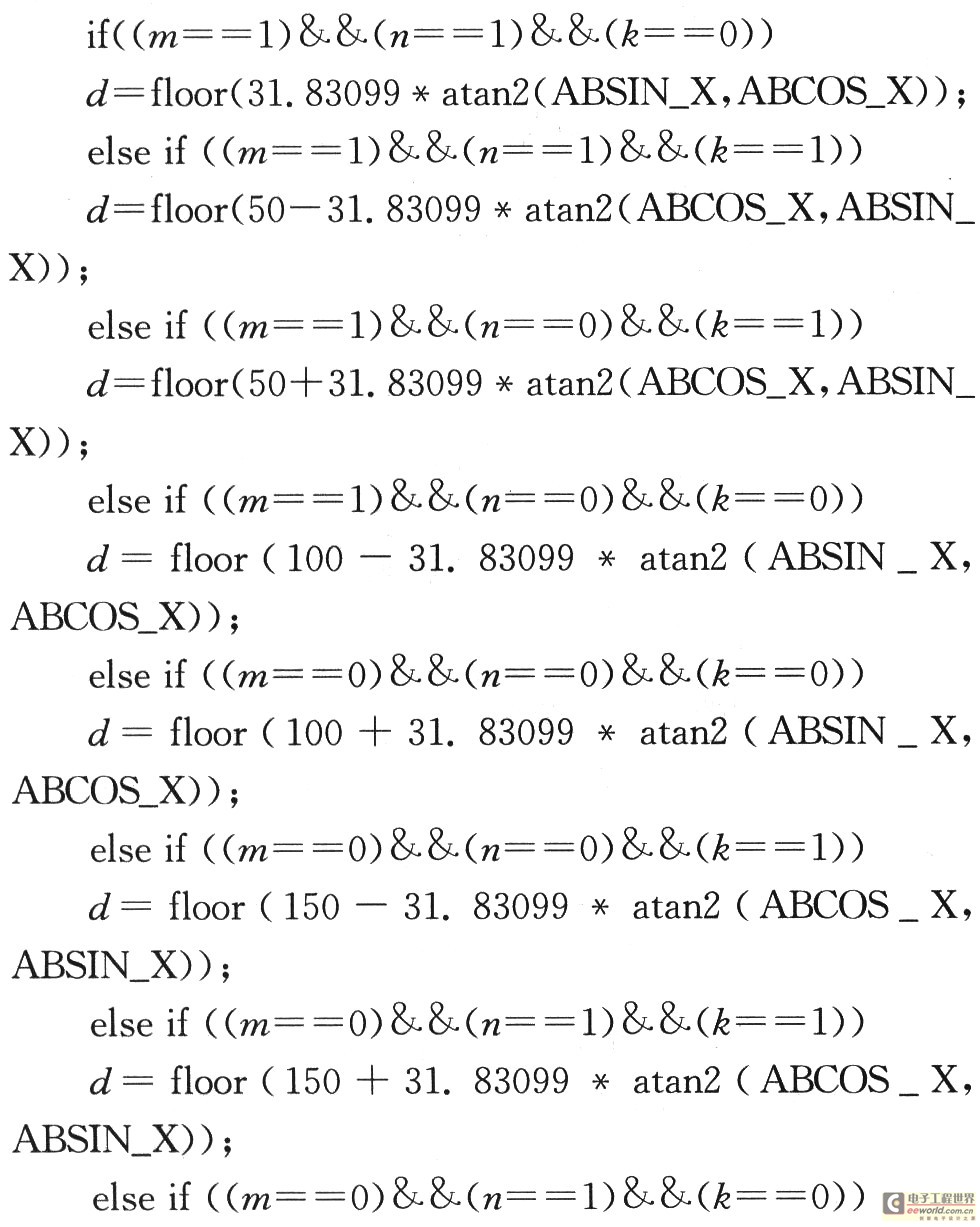

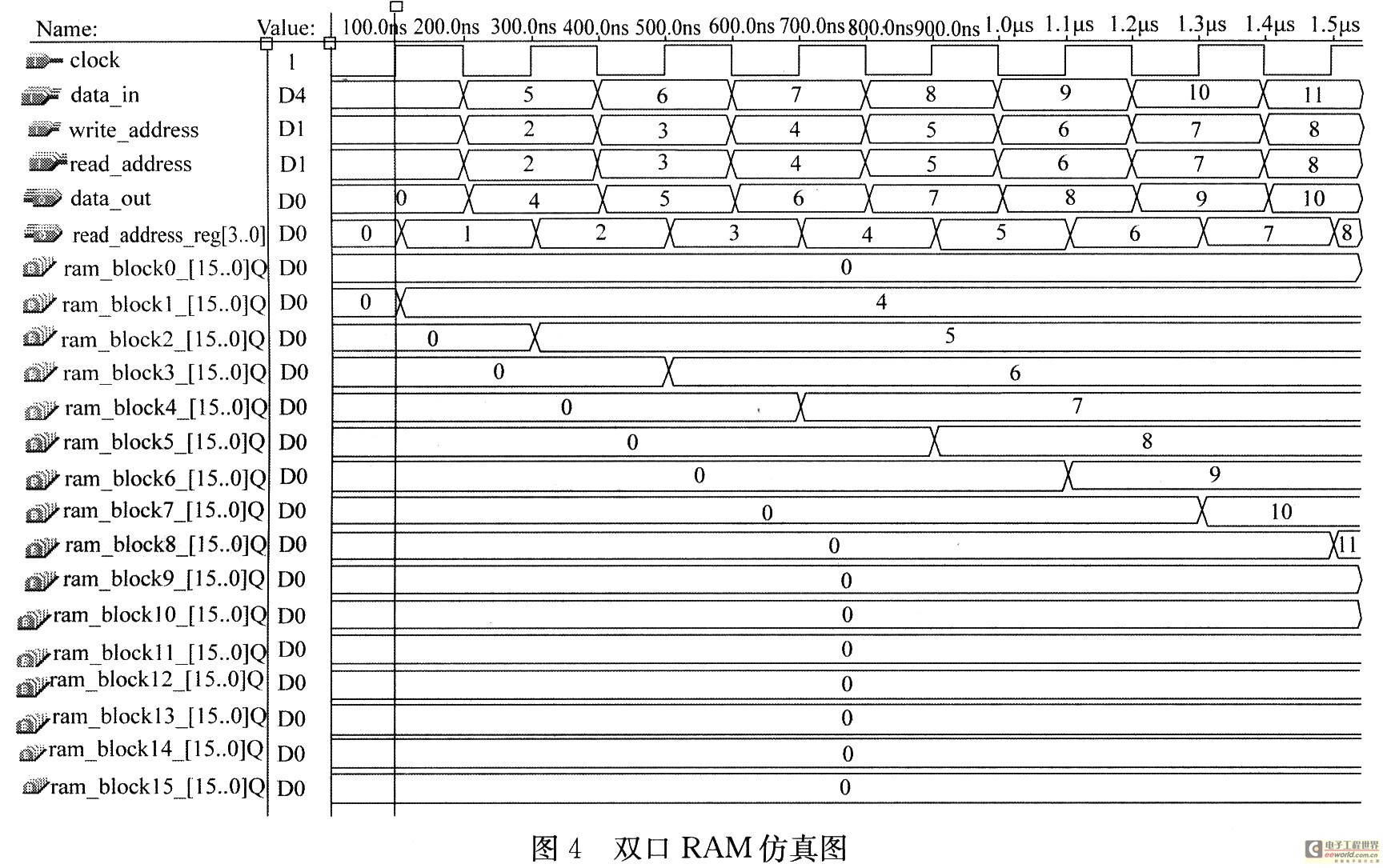

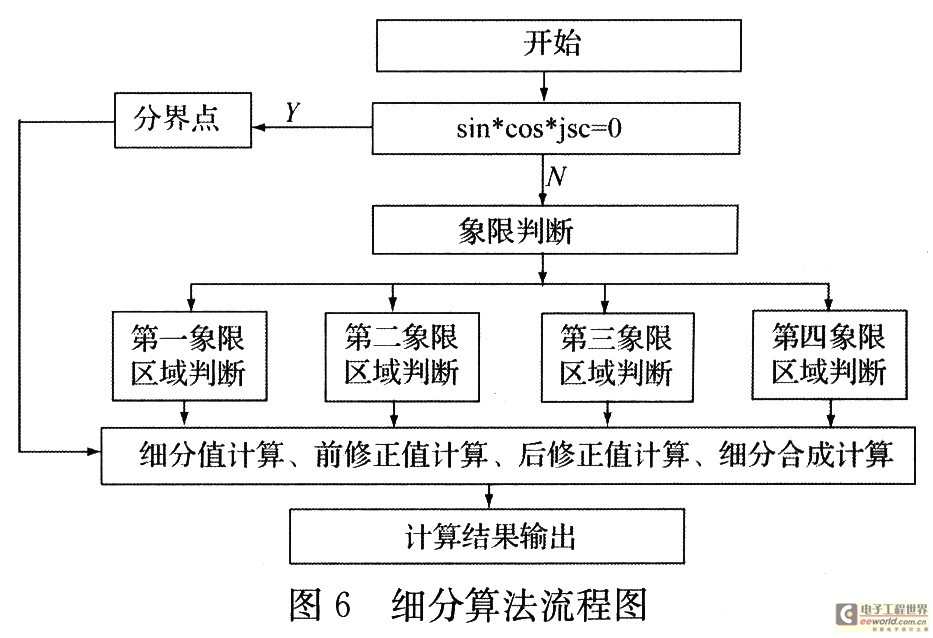

其中细分方法也就是对K值的求取采用了八卦限幅值分割法,根据上述方法设计了细分倍数可变的细分算法,利用DSP C语言的专用库函数实现了纯计算的算法。细分算法流程如图6所示。

由幅值细分法可知,软件细分算法设计的关键问题是根据两路信号的比值对该点的相位角的正确定位。该点的位置有两种情况,一种是落在各象限的边界上,另一种是落在各象限之中。根据细分边界条件判断该点的采样数据是否发生在四个象限的分界线上,如果判断此次换向发生在象限的分界线上,则细分数为固定值,并且通过象限的正负关系就可以确定具体细分数值,不需要进行复杂的计算。如果该点不是发生在象限分界线上,则需根据象限正负关系判断换向发生的具体象限,不同象限对应不同计算公式。细分算法程序如下:

static int subdiv(int*input,int*input1)一设置指针形参用来读取两路波形采样值

{

程序初始化,定义各种变量标志字。

float ADSIN_X,ADCOS_X,ABSIN_X,ABCOS_X;一定义存储变量存放采样值与绝对值

int m=0,n=0,k=0,d=0,i=0;一设置标志字判断采样值正负

ADSIN_X=*input;-从缓存区读取sin采样值

ADCOS_X=*input1;-从缓存区读取cos采样值

ABSIN_X=fabs(ADSIN_X);-求取sin绝对值

ABCOS_X=fabs(ADCOS_X);-求取COS绝对值

根据采样值,写标志字

if(ADSIN_X>0) m=1; else m=0;

if(ADCOS_X>0) n=1; else n=0;

if((ABSIN_X-ABCOS_X)>0)k=1;else if((AB-SIN_X-ABCOS_X)<O) k=0;

elsek=2;

根据标志字判断相位点的位置,根据相应位置不同公式求取细分值

|

|

然后利用公式R=N×ω+d×L求出任意一点谐振子的幅值并输出。式中N为整周期的累加计数值,W为光栅栅距,d为细分计数,L=ω/m,m为细分倍数。

5 结束语

设计的光栅地震检波器充分结合了FPGA的强大控制功能和DSP高速运算处理功能,实现了信号的同步采集、高倍细分和实时复现。减少了单一处理器的负荷,提高了系统的速度和稳定性,为光栅震动信号处理提出了一个新思路。由于硬件双口RAM接口时序复杂,成本高也会给系统带来不稳定性,因此本文在FPGA中设计了一软RAM。对于振动信号幅值的计算则是在对整周期的莫尔条纹进行计数的同时,利用软件细分法实时地计算出非整周期的莫尔条纹信号所代表的小数值,并实时将二者相加后乘以莫尔条纹当量(每个莫尔条纹所代表的位移量),即可得到信号的实时振动幅值。

电子 DSP FPGA 传感器 VHDL ADC 放大器 滤波器 电路 电压 C语言 仿真 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)