针对GPON突发模式接收器的低功耗FPGA方案

时间:11-09

来源:互联网

点击:

带服务能够支持三重应用(即支持语音、视频和数据)至第一英里的客户,例如持续发展的小商业和住宅。FTTx中的主角是GPON(吉比特无源光网络,Gigabit Passive Optical Network),它提供较高的带宽替代DSL和电缆的基于光纤的网络。FTTx为家庭的第一英里应用,诸如光纤到户(FTTH),光纤到楼(FTTB),光纤到路边(FTTC)等。随着下行数据速率高达2.5Gbps,以及改进现存的电信设施的需求,针对这些第一英里的应用,GPON网络是受欢迎的选择。由于有效地增加了带宽,预计GPON会超过EPON(以太无源光网络,Ethernet Passive Optical Network),因此会选择GPON作为将来第一英里网络的技术。

GPON功能一览

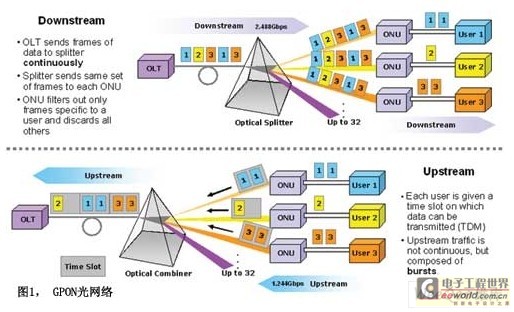

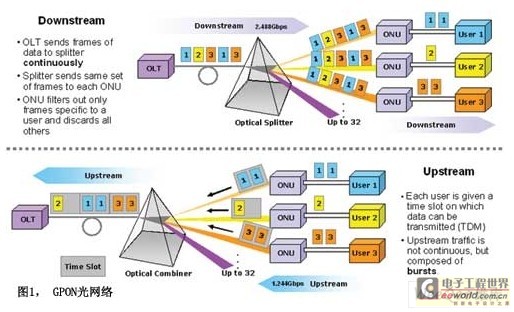

GPON是时分复用(TDM)系统,基于现存设施的再使用,从远端传送数据时,时隙分配给了终端用户。如图1所示,在GPON中有两个主要的数据流。下行方向从OLT(光线路终端,Optical Line Terminal)到光分路器,传播数据到多个ONU(光网络单元,Optical Network Units)。在上行方向,这个过程相反。给每个用户(ONU)分配一个时隙以便传送数据,随后在单根光纤上与其它数据结合在一起发送到中央办公设备(OLT)。ONU是互相分开的,ONU源数据是由突发数据组成的,由于多个ONU的不同光长度,在上行数据里内部的相位有变化,并将发生冲突。OLT的挑战是修正每个ONU的排列,并确保在上行光链路中每个突发数据同步。

在OLT中,上行通路处理这些高速突发数据的锁定时间要求是很有挑战性的(对GPON的典型值为50比特),然而传统的XAUI或基于SERDES的SONET/SDH的锁定时间很长(数千比特)。结果客户不得不使用特殊的,分立的突发模式接收器(BMR)。然而传统的BMR消耗很大的功率,且难以升级,导致无法优化体积,最终增加了系统的成本。

迄今为止对这些特殊的BMR还没有特殊的解决方案。然而随着FPGA的出现,它们支持快速锁定,执行时间短,集成的BMR功能支持达2Gbps的速度。

理想的BMR

如前所述,为了处理上行通路的动态性质,BMR必须满足一组特定的要求。理想的BMR应有非常快的锁定时间,支持高速串行数据速率,同时又保持最小的尺寸和最小的功耗。传统的BMR已提供了针对GPON的数据速率,但在成本、功耗和电路板的面积方面做了一些折衷。另外一方面,过去FPGA提供灵活性和很高的集成度,但这些FPGA的SERDES不能满足GPON所要求的锁定时间和数据速率的要求。理想的解决方案取决于BMR和FPGA。现在的解决方案是目前FPGA的I/O能力。这些编程平台的独特功能是在每个引脚上端接上行PON通路,与传统的BMR器件相比较,提供了节省成本和可升级的解决方案。目前使用的最普通的方法是用FPGA采样输入数据。

这个方法所关注的是性能和功耗。FPGA对PON终端提供了另外一种方法,这种FPGA是LatticeSC系列。这些器件通过合并每个I/O内的特殊逻辑来应对BMR的挑战,可动态地适应不同的线而无需使用FPGA逻辑。

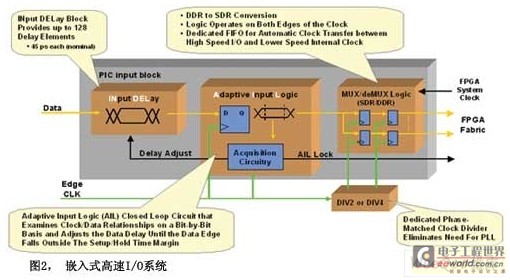

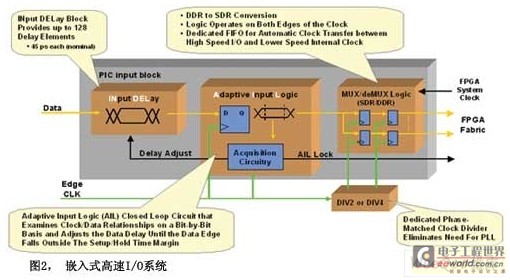

如图2所示,嵌入在每个I/O中的是输入延时块(INDEL)和自适应输入逻辑(AIL),动态地补偿时序相位变化,使每个引脚的速度达2Gbps。终端的结果是完整的I/O系统,支持快速锁定时间和传统BMR的性能,但具有很高的集成度,而且是低功耗的编程平台。

如何进行AIL相位修正

传统的BMR使用时钟数据恢复(CDR)在OLT中产生上行采样时钟。如前所述,用于GPON应用的时钟方法要求专用的大功率电路,以满足挑战性的速度和上行通路的锁定时间要求。因为GPON的物理层是基于现有的TDM设备,GPON其本身的性质是时间环,意为在OLT本地的参考时钟可以作为参考时钟来采样输入数据。AIL利用这个本地OLT时钟源产生本地的625MHz时钟。这个时钟用来对输入数据采样,对连续突发模式进行动态延时,端接多个ONU时补偿上行通路的相位变化。

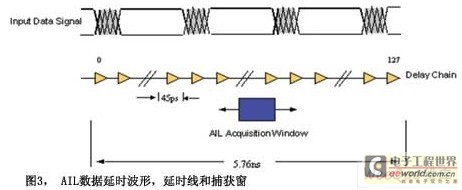

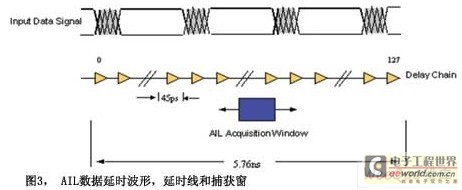

128个抽头的延时(每个45ps)使能多个输入数据的连续周期,在延时链路中任何时间都能进行采样。自适应输入逻辑(AIL)监控这个输入数据的多个采样,动态调整时钟,数据相位关系,直到找到有效的采样点。含有数据、转换、抖动和噪声的输入数据信号通过延时链路。于是AIL通过延时链滑动捕获窗,根据单独的数据转换寻找稳定的数据。一旦发现稳定的数据,AIL将继续监控输入和数据,动态补偿由于工艺、电压和温度而引起的低频抖动,漂移和变化。用延时链建立数据的多个复本的新方法提供了比用高速时钟采样数据功耗低的解决方案。图3为对AIL方法的观察。

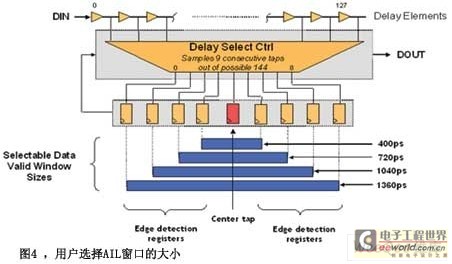

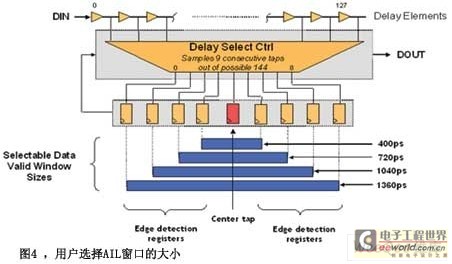

AIL窗用来从延时链获取采样数据。这个窗含有边沿检测寄存器和中心抽头采样寄存器。中心抽头寄存器是采样到数据的实际寄存器,随后再送到FPGA。边沿检测寄存器是窗的“眼睛和耳朵”,因为其反馈提供了进行研究算法的信息。在最大的窗,采样寄存器的每个边有4个边沿检测寄存器。图4展示了AIL窗的寄存器分布和窗的大小。

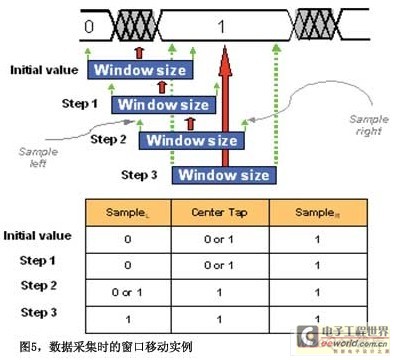

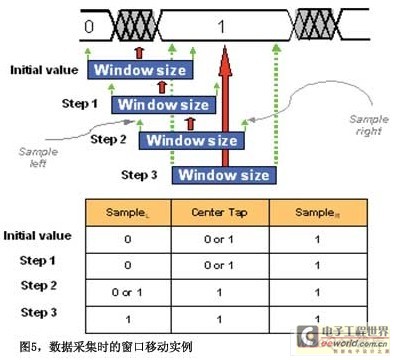

最坏的捕获时间是窗口的中心正对数据转换时。于是窗口开始搜索无噪声的数据,比较从边沿检测采样到的数据和中心抽头寄存器的数据。根据这些值,窗口以90ps步长单方向地连续移动,直到找到稳定的数据。一旦找到稳定的数据,AIL继续跟踪时钟,数据相位关系,补偿低速抖动,漂移以及工艺、电压和温度的变化。图5展示了搜索过程。

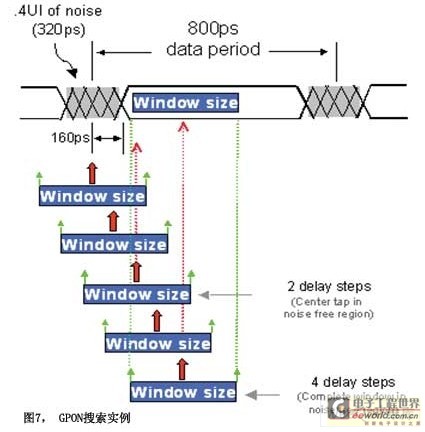

通过计算最差情况的数据有效时期来确定窗口的大小,如图6所示。用户选择最大的窗以适配计算出最坏情况窗。例如,上行GPON应用中数据时期为800ps。GPON规范允许的抖动为0.4UI,结果数据有效时期为480ps (800ps"320ps)。因此,从所提供的GUI中选择400ps的窗口尺寸。

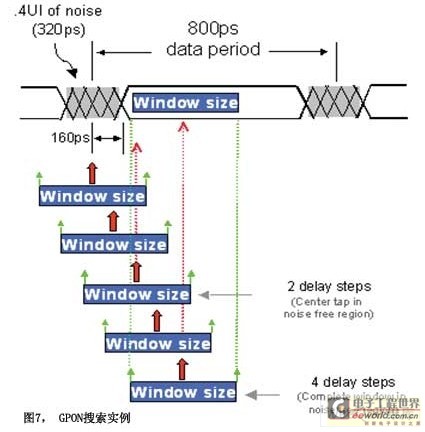

一旦确定了窗口大小,就可以考虑窗口的移动。对AIL捕获的最差情况是必须解决160ps抖动,即转换中心的起始点,如图7所示。根据90ps步长,针对AIL采用有效数据的中心抽头寄存器要用2个延时步长(180ps),针对在无噪声环境中的整个窗口,要4个延时步长。记住用户从中心抽头寄存器看到数据,因此对于用户接收,检测有效数据,不需要整个窗在在无噪声的环境中。因为每个延时步长,AIL需要4个转换,在8个数据转换之后,用户会看到有效的中心抽头数据,在16个数据转换内整个窗在无噪声的环境中。针对初始数据采集时间,两者皆好且符合GPON规范。

GPON功能一览

GPON是时分复用(TDM)系统,基于现存设施的再使用,从远端传送数据时,时隙分配给了终端用户。如图1所示,在GPON中有两个主要的数据流。下行方向从OLT(光线路终端,Optical Line Terminal)到光分路器,传播数据到多个ONU(光网络单元,Optical Network Units)。在上行方向,这个过程相反。给每个用户(ONU)分配一个时隙以便传送数据,随后在单根光纤上与其它数据结合在一起发送到中央办公设备(OLT)。ONU是互相分开的,ONU源数据是由突发数据组成的,由于多个ONU的不同光长度,在上行数据里内部的相位有变化,并将发生冲突。OLT的挑战是修正每个ONU的排列,并确保在上行光链路中每个突发数据同步。

在OLT中,上行通路处理这些高速突发数据的锁定时间要求是很有挑战性的(对GPON的典型值为50比特),然而传统的XAUI或基于SERDES的SONET/SDH的锁定时间很长(数千比特)。结果客户不得不使用特殊的,分立的突发模式接收器(BMR)。然而传统的BMR消耗很大的功率,且难以升级,导致无法优化体积,最终增加了系统的成本。

迄今为止对这些特殊的BMR还没有特殊的解决方案。然而随着FPGA的出现,它们支持快速锁定,执行时间短,集成的BMR功能支持达2Gbps的速度。

理想的BMR

如前所述,为了处理上行通路的动态性质,BMR必须满足一组特定的要求。理想的BMR应有非常快的锁定时间,支持高速串行数据速率,同时又保持最小的尺寸和最小的功耗。传统的BMR已提供了针对GPON的数据速率,但在成本、功耗和电路板的面积方面做了一些折衷。另外一方面,过去FPGA提供灵活性和很高的集成度,但这些FPGA的SERDES不能满足GPON所要求的锁定时间和数据速率的要求。理想的解决方案取决于BMR和FPGA。现在的解决方案是目前FPGA的I/O能力。这些编程平台的独特功能是在每个引脚上端接上行PON通路,与传统的BMR器件相比较,提供了节省成本和可升级的解决方案。目前使用的最普通的方法是用FPGA采样输入数据。

这个方法所关注的是性能和功耗。FPGA对PON终端提供了另外一种方法,这种FPGA是LatticeSC系列。这些器件通过合并每个I/O内的特殊逻辑来应对BMR的挑战,可动态地适应不同的线而无需使用FPGA逻辑。

如图2所示,嵌入在每个I/O中的是输入延时块(INDEL)和自适应输入逻辑(AIL),动态地补偿时序相位变化,使每个引脚的速度达2Gbps。终端的结果是完整的I/O系统,支持快速锁定时间和传统BMR的性能,但具有很高的集成度,而且是低功耗的编程平台。

如何进行AIL相位修正

传统的BMR使用时钟数据恢复(CDR)在OLT中产生上行采样时钟。如前所述,用于GPON应用的时钟方法要求专用的大功率电路,以满足挑战性的速度和上行通路的锁定时间要求。因为GPON的物理层是基于现有的TDM设备,GPON其本身的性质是时间环,意为在OLT本地的参考时钟可以作为参考时钟来采样输入数据。AIL利用这个本地OLT时钟源产生本地的625MHz时钟。这个时钟用来对输入数据采样,对连续突发模式进行动态延时,端接多个ONU时补偿上行通路的相位变化。

128个抽头的延时(每个45ps)使能多个输入数据的连续周期,在延时链路中任何时间都能进行采样。自适应输入逻辑(AIL)监控这个输入数据的多个采样,动态调整时钟,数据相位关系,直到找到有效的采样点。含有数据、转换、抖动和噪声的输入数据信号通过延时链路。于是AIL通过延时链滑动捕获窗,根据单独的数据转换寻找稳定的数据。一旦发现稳定的数据,AIL将继续监控输入和数据,动态补偿由于工艺、电压和温度而引起的低频抖动,漂移和变化。用延时链建立数据的多个复本的新方法提供了比用高速时钟采样数据功耗低的解决方案。图3为对AIL方法的观察。

AIL窗用来从延时链获取采样数据。这个窗含有边沿检测寄存器和中心抽头采样寄存器。中心抽头寄存器是采样到数据的实际寄存器,随后再送到FPGA。边沿检测寄存器是窗的“眼睛和耳朵”,因为其反馈提供了进行研究算法的信息。在最大的窗,采样寄存器的每个边有4个边沿检测寄存器。图4展示了AIL窗的寄存器分布和窗的大小。

最坏的捕获时间是窗口的中心正对数据转换时。于是窗口开始搜索无噪声的数据,比较从边沿检测采样到的数据和中心抽头寄存器的数据。根据这些值,窗口以90ps步长单方向地连续移动,直到找到稳定的数据。一旦找到稳定的数据,AIL继续跟踪时钟,数据相位关系,补偿低速抖动,漂移以及工艺、电压和温度的变化。图5展示了搜索过程。

通过计算最差情况的数据有效时期来确定窗口的大小,如图6所示。用户选择最大的窗以适配计算出最坏情况窗。例如,上行GPON应用中数据时期为800ps。GPON规范允许的抖动为0.4UI,结果数据有效时期为480ps (800ps"320ps)。因此,从所提供的GUI中选择400ps的窗口尺寸。

一旦确定了窗口大小,就可以考虑窗口的移动。对AIL捕获的最差情况是必须解决160ps抖动,即转换中心的起始点,如图7所示。根据90ps步长,针对AIL采用有效数据的中心抽头寄存器要用2个延时步长(180ps),针对在无噪声环境中的整个窗口,要4个延时步长。记住用户从中心抽头寄存器看到数据,因此对于用户接收,检测有效数据,不需要整个窗在在无噪声的环境中。因为每个延时步长,AIL需要4个转换,在8个数据转换之后,用户会看到有效的中心抽头数据,在16个数据转换内整个窗在无噪声的环境中。针对初始数据采集时间,两者皆好且符合GPON规范。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)