图像自适应分段线性拉伸算法的FPGA设计

时间:11-09

来源:互联网

点击:

由于红外图像的成像机理以及红外成像自身的原因,红外图像有对比度低、图像较模糊、噪声大等特点。因此抑止噪声,提高图像信噪比,以及调整红外图像对比度,以利于后续图像分析、目标识别或跟踪,必须对红外图像进行增强处理。另外,在其他场合,若采用人机交互方式,则必须对原始图像进行预处理,改善图像视觉效果,使其更适合人机进一步的分析和处理。

图像增强从作用域出发,分为空间域增强和频率域增强两种。频率域是一种间接增强的方法,由于存在域之间的变换和反变换,计算复杂,难以满足实时性要求。自适应分段线性拉伸算法是一种空间域图像增强方法,直接对图像像素灰度进行操作,由于运算过程简单、实现方便,目前的图像增强预处理电路大多选用这种算法。硬件实现上,最初是采用单片DSP芯片实现,其原理为:图像数据实时的传输给DSP,DSP接收完1块数据后,再对整块数据进行增强处理,这样势必会造成时间的延迟,不能满足精确制导武器系统实时性的要求。后来硬件结构发展为采取DSP,FPGA芯片相结合的方式。这样,有效结合了DSP的运算能力强与FPGA逻辑和存储资源丰富的优点;不足之处在于,DSP与FPGA之间的通信给设计工作增加了额外负担。与DSP相比,FPGA结构上的优势使得其更适合完成并行处理、及结构性强和高速的运算。本文基于这种算法理论基础,使用xilinx公司规模较大的XC4VLXl5系列FPGA,实现了红外图像的实时处理。

1 自适应线性分段线性灰度级拉伸算法

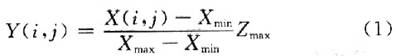

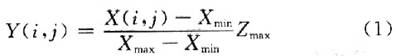

图像灰度线性拉伸算法表达式为:

式中:i是图像数据行号;j是图像数据列号;Y(i,J)是拉伸后输出图像灰度值;X(i,j)是输入原始图像灰度值,为14 b二进制数;Xmin是输入图像数据的最小灰度值;Xmax是输入图像数据的最大灰度值;Zmax表明输出图像的最大灰度值,设计中拉伸后的图像灰度值用8 b二进制数表示,故Zmax=255。

首先对红外图像做灰度直方图统计,低信噪比条件下,选取压缩因子为5%,将盲元和噪声的影响降到最低。分别搜索5%最大灰度值中的最小值作为Xmax,5%最小灰度值里的最大值作为Xmin。拉伸转换时,将大于Xmax的像素灰度置为Zmax,小于Xmin的像素灰度置为O。此算法将线性拉伸区间自适应地分为[O,Xmin),[Xmin,Xmax]和(Xmax,255]三个部分。其中,[O,Xmin)和(Xmax,255]两个灰度区间的像素灰度分别被压缩为O和255。若图像中目标较小,且目标正好位于两个被压缩的区间内,就有可能被抑制。为避免这种情况发生,可视情况适当调整压缩因子5%的大小。

2 拉伸算法的FPGA实现

2.1 设计思路

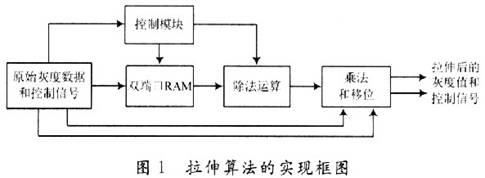

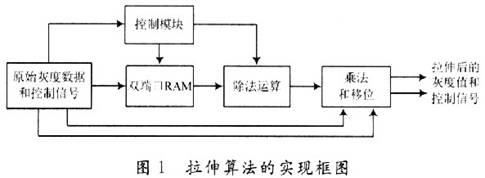

根据以上算法分析,FPGA设计思路如下:在每帧图像帧正程,用双端口RAM进行直方图统计,记录每个像素灰度值出现的次数,帧逆程即可统计得到此帧图像的Xmin和Xmax。因为相邻两帧图像近似度高,可用前帧得到的Xmin和Xmax来处理下帧图像。在帧逆程时,调用除法器计算出

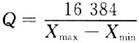

的值;在下帧正程时,只需计算Q·[X(i,j)-Xmin],然后将得到的结果除以64(左移6位),即对每个像素只需1次减法、1次乘法和移位就可完成拉伸运算。实现框图如图1所示,拉伸后数据的输出仅比输入延时62.5 ns,实现了对红外图像的实时处理。

2.2 硬件设计

通过以上设计思路的分析,设计主要包括灰度直方图统计、除法和拉伸运算3部分。下面进行详细介绍。

2.2.1 双端口RAM

XC4VLXl5芯片具有丰富的BlockRAM资源,用它构成双端口RAM,进行灰度直方图统计。像素的灰度值作为双端口RAM的地址,对应空间存储此灰度值在1帧图像里的频数。以320×256帧大小、灰度值为14 b的红外图像为例,在每个像素灰度值都相同的极限情况下,每个地址空间需要的存储的值为81 920,转换为二进制有17 b,故所需存储空间大小为17 b×214。对双端口RAM的操作分为三个阶段:

(1)在帧正程时,只需对A端口进行读/写操作。根据接收到的像素灰度值,先读出RAM中对应地址空间的储值,加“1”后回写入原来的地址空间,这样在每帧正程结束时,就统计完了每个灰度值出现的频数,即完成了灰度直方图统计。

(2)帧逆程时,要同时对A,B端口进行读操作。对于A端口,依次从高地址读取RAM中的数,将读取的数进行累加,当和大于帧像素个数的5%时,此时对应的地址值即为Xmax;类似地对B端口操作,从0地址开始读RAM,可找到Xmin。将得到的灰度值Xmin和Xmax存入寄存器,作为除法器和下一帧图像拉伸运算的输入。

(3)每帧最后将双端口RAM清零,为下一帧灰度直方图统计做准备。由于双端口RAM没有整体清零功能,设计中采用从“O”地址开始。依次往高地址写零的方式清零。

2.2.2 除法器

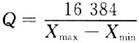

除法运算通过调用ISE IP Core Generator生成的15位定点除法器来实现,满足高精度要求,而不采用逼近法。一帧图像的拉伸只需调用一次除法器,提高了运算的效率。在帧逆程计算Q:=16 384/(Xmax-Xmin)的值,对于15位输入,除法器有18个时钟周期的延时,而这并不会影响图像处理的实时性。

2.2.3 控制时钟

在1个像素时钟周期内要完成读RAM、加法计算和回写RAM的操作,RAM的控制时钟至少必须是像素时钟的4倍。控制时钟的选取还要考虑帧逆程的时间长度,要在逆程里访问RAM查找到Xmin和Xmax,还要完成RAM清零操作。FPGA系统时钟为96 MHz,分频后产生48 MHz,为像素时钟8倍,用它作为双端口RAM和除法器的控制时钟,可满足要求。

2.2.4 拉伸运算

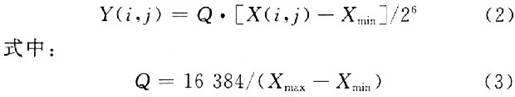

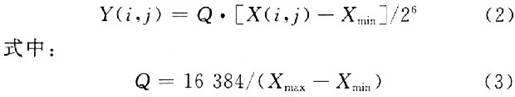

将式(1)进行简单变换,可以记为:

Q值在上帧结束前已经得到,根据式(2)拉伸运算得到简化,只需1次减法和乘法运算,得到积的小数点左移6位后,截取低8位就得到拉伸后的灰度值。需要注意的是,截取前要判定乘法是否溢出,如果溢出,结果置为最大灰度值255。

图像增强从作用域出发,分为空间域增强和频率域增强两种。频率域是一种间接增强的方法,由于存在域之间的变换和反变换,计算复杂,难以满足实时性要求。自适应分段线性拉伸算法是一种空间域图像增强方法,直接对图像像素灰度进行操作,由于运算过程简单、实现方便,目前的图像增强预处理电路大多选用这种算法。硬件实现上,最初是采用单片DSP芯片实现,其原理为:图像数据实时的传输给DSP,DSP接收完1块数据后,再对整块数据进行增强处理,这样势必会造成时间的延迟,不能满足精确制导武器系统实时性的要求。后来硬件结构发展为采取DSP,FPGA芯片相结合的方式。这样,有效结合了DSP的运算能力强与FPGA逻辑和存储资源丰富的优点;不足之处在于,DSP与FPGA之间的通信给设计工作增加了额外负担。与DSP相比,FPGA结构上的优势使得其更适合完成并行处理、及结构性强和高速的运算。本文基于这种算法理论基础,使用xilinx公司规模较大的XC4VLXl5系列FPGA,实现了红外图像的实时处理。

1 自适应线性分段线性灰度级拉伸算法

图像灰度线性拉伸算法表达式为:

式中:i是图像数据行号;j是图像数据列号;Y(i,J)是拉伸后输出图像灰度值;X(i,j)是输入原始图像灰度值,为14 b二进制数;Xmin是输入图像数据的最小灰度值;Xmax是输入图像数据的最大灰度值;Zmax表明输出图像的最大灰度值,设计中拉伸后的图像灰度值用8 b二进制数表示,故Zmax=255。

首先对红外图像做灰度直方图统计,低信噪比条件下,选取压缩因子为5%,将盲元和噪声的影响降到最低。分别搜索5%最大灰度值中的最小值作为Xmax,5%最小灰度值里的最大值作为Xmin。拉伸转换时,将大于Xmax的像素灰度置为Zmax,小于Xmin的像素灰度置为O。此算法将线性拉伸区间自适应地分为[O,Xmin),[Xmin,Xmax]和(Xmax,255]三个部分。其中,[O,Xmin)和(Xmax,255]两个灰度区间的像素灰度分别被压缩为O和255。若图像中目标较小,且目标正好位于两个被压缩的区间内,就有可能被抑制。为避免这种情况发生,可视情况适当调整压缩因子5%的大小。

2 拉伸算法的FPGA实现

2.1 设计思路

根据以上算法分析,FPGA设计思路如下:在每帧图像帧正程,用双端口RAM进行直方图统计,记录每个像素灰度值出现的次数,帧逆程即可统计得到此帧图像的Xmin和Xmax。因为相邻两帧图像近似度高,可用前帧得到的Xmin和Xmax来处理下帧图像。在帧逆程时,调用除法器计算出

的值;在下帧正程时,只需计算Q·[X(i,j)-Xmin],然后将得到的结果除以64(左移6位),即对每个像素只需1次减法、1次乘法和移位就可完成拉伸运算。实现框图如图1所示,拉伸后数据的输出仅比输入延时62.5 ns,实现了对红外图像的实时处理。

2.2 硬件设计

通过以上设计思路的分析,设计主要包括灰度直方图统计、除法和拉伸运算3部分。下面进行详细介绍。

2.2.1 双端口RAM

XC4VLXl5芯片具有丰富的BlockRAM资源,用它构成双端口RAM,进行灰度直方图统计。像素的灰度值作为双端口RAM的地址,对应空间存储此灰度值在1帧图像里的频数。以320×256帧大小、灰度值为14 b的红外图像为例,在每个像素灰度值都相同的极限情况下,每个地址空间需要的存储的值为81 920,转换为二进制有17 b,故所需存储空间大小为17 b×214。对双端口RAM的操作分为三个阶段:

(1)在帧正程时,只需对A端口进行读/写操作。根据接收到的像素灰度值,先读出RAM中对应地址空间的储值,加“1”后回写入原来的地址空间,这样在每帧正程结束时,就统计完了每个灰度值出现的频数,即完成了灰度直方图统计。

(2)帧逆程时,要同时对A,B端口进行读操作。对于A端口,依次从高地址读取RAM中的数,将读取的数进行累加,当和大于帧像素个数的5%时,此时对应的地址值即为Xmax;类似地对B端口操作,从0地址开始读RAM,可找到Xmin。将得到的灰度值Xmin和Xmax存入寄存器,作为除法器和下一帧图像拉伸运算的输入。

(3)每帧最后将双端口RAM清零,为下一帧灰度直方图统计做准备。由于双端口RAM没有整体清零功能,设计中采用从“O”地址开始。依次往高地址写零的方式清零。

2.2.2 除法器

除法运算通过调用ISE IP Core Generator生成的15位定点除法器来实现,满足高精度要求,而不采用逼近法。一帧图像的拉伸只需调用一次除法器,提高了运算的效率。在帧逆程计算Q:=16 384/(Xmax-Xmin)的值,对于15位输入,除法器有18个时钟周期的延时,而这并不会影响图像处理的实时性。

2.2.3 控制时钟

在1个像素时钟周期内要完成读RAM、加法计算和回写RAM的操作,RAM的控制时钟至少必须是像素时钟的4倍。控制时钟的选取还要考虑帧逆程的时间长度,要在逆程里访问RAM查找到Xmin和Xmax,还要完成RAM清零操作。FPGA系统时钟为96 MHz,分频后产生48 MHz,为像素时钟8倍,用它作为双端口RAM和除法器的控制时钟,可满足要求。

2.2.4 拉伸运算

将式(1)进行简单变换,可以记为:

Q值在上帧结束前已经得到,根据式(2)拉伸运算得到简化,只需1次减法和乘法运算,得到积的小数点左移6位后,截取低8位就得到拉伸后的灰度值。需要注意的是,截取前要判定乘法是否溢出,如果溢出,结果置为最大灰度值255。

- 基于FPGA的远程图像采集系统设计(11-23)

- Actel数模结合FPGA的远程控制器设计(05-13)

- 基于FPGA的二值图像连通域标记快速算法实现(07-24)

- 关于CPLD和接触式图像传感器的图像采集系统(07-26)

- FPGA的光电抗干扰电路设计(08-07)

- StrongARM及其嵌入式应用平台(08-30)