基于GAP技术的网络隔离设备的研究与设计

时间:11-09

来源:互联网

点击:

- D、TESI UNIT READY、INQUIRY、REQUEST、SENSE、READ CAPACITY后都将进入数据进相序。此时目标器将MSG和C/D信号置为无效,将I/O信号置为有效。目标器将发送相应的数据。在命令为WRITE后将进入数据出阶段,此时目标器将MSG、C/D和I/O都置为O,启动器向目标器发送数据,之后进入消息阶段。

- Status模块处理状态阶段的时序。在命令完成后将进入状态阶段,目标器将MSG信号置为无效,将C/D和I/O信号置为有效,并发送命令执行的情况是GOOD还是CHECK CONDITON。状态阶段结束后将进入消息进阶段,向启动器说明一个COM-MAND COMPLETED。至此一个SCSI访问结束。目标器将进入空闲阶段,启动器将可以通过1个80 H的消息触发另外一个访问。

- Msg_in模块处理消息进阶段的消息发送时序。目标器接收到16位宽传输的消息后将进入消息进时序。目标器将MSG、C/D以及I/O都置为有效,并发送重复的信息。发送完后目标器将释放MSG信号,并根据消息确定下一个阶段。

3.3 SDRAM IP核的应用

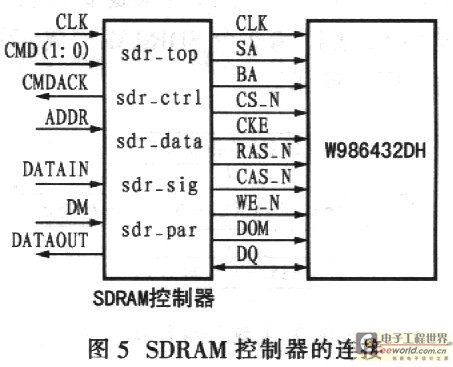

SDRAM是一种高速同步动态随机存储器,在嵌入式系统中,SDRAM因其价格低、体积小、速度快,容量大等优点而逐渐成为一种主流器件,但SDRAM的控制逻辑复杂,时序严格,使用不便,需要控制器提供正确命令来完成其初始化、读写和刷新等工作。SDRAM控制器根据SDRAM的内部状态转化图进行设计,而且很多大公司都提供标准SDRAM控制器的IP核参考设计。笔者选用了WINBOND公司的W986432DH型SDRAM,它采用512 Kx4x32位架构,由4个BANK构成,每个BANK对应4 M字节,按行和列寻址,W986432DH的引脚分为控制、地址和数据信号三类。其控制器选用LatTIce公司的标准SDR SDRAM IP核,由4个底层模块sdr_ctrl、sdr_sig、sdr_data、sdr_par和顶层模块sdr_top组成,如图5所示。

8dr_ctrl模块根据SDRAM内部状态转化关系建立2个有限状态机和1个计数器,能产生正确的中间状态作为sdr_sig模块输入。sdr_sig模块产生面向SDRAM的控制、地址信号。sdr_data模块实现FPGA与SDRAM之间的数据传输。sdr_par模块完成猝发长度,延时节拍等参数设置,通过在该模块中设置不同的参数来满足不同的应用系统。

sdr__top将底层4个模块整合成1个可以调用的系统。整个IP核类似于黑匣子,不用详细了解其内部实现细节,只需了解左边控制信号的含义,对SDRAM的不同操作通过改变左边控制信号的状态即可。

4 结束语

本文提出了基于GAP技术的网络保护设备设计新方案,阐述了主要模块的实现方法,限于篇幅不能给出具体细节和源代码。采用1个FPGA替代单片机和SCSI协议控制器,可减少电路数量,降低成本,便于升级。

电子 电路 FPGA LTE 电压 嵌入式 总线 单片机 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)