基于SOPC的通用TFT-LCD控制器IP核设计

时间:11-09

来源:互联网

点击:

随着电子技术的迅猛发展,液晶显示器(LCD)具有功耗低,体积小,重量轻,超薄等许多其他显示器无法比拟的优点,被广泛用于智能仪器、仪表和低功耗电子产品中。TFT-LCD屏采用有源显示方式,具有抗抖动,色彩饱和度高,还原能力强和对比度高等特点,在嵌入式系统中具有广泛的应用前景。在嵌入式系统中,LCD控制器是处理器与LCD显示驱动器之间的接口部件,对LCD屏提供时序信号和显示数据,用来控制数据在LCD屏幕上的显示,是LCD系统中重要的组成部分。现有的LCD控制器一般都由各个生产厂家自行开发,通用性差,而软件控制TFT-LCD会占用大量的处理器资源,使得系统的集成度不高。

SoPCBuilder是Altera公司实现SoPC概念的一款工具软件,使得用户可以通过自定义逻辑的方法方便地开发基于NiosⅡ的SoPC系统。So-PCBuilder集成在EDA工具QuartusⅡ中,提供NiosⅡ处理器及一些常用外设接口,用于组建一个在模块级和组件级定义的系统,能够自动生成片上总线和总线仲裁器等所需的逻辑。基于SoPC的设计在很大程度上依赖于利用集成电路IP(intellectualproperty)。集成电路IP是指经过预先设计、预先验证、符合产业界普遍认同的设计规范和设计标准,具有相对独立,并可以重复利用的电路模块或子系统。本文中提出一种基于SoPC的参数化TFT-LCD控制器IP核设计,用硬件描述语言实现控制器的逻辑功能,这种参数化的组件设计具有很强的通用性和兼容性。

1 通用册LCD控制器总体设计

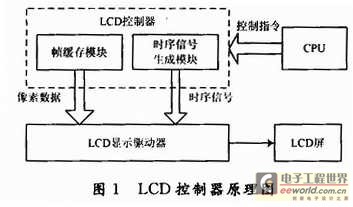

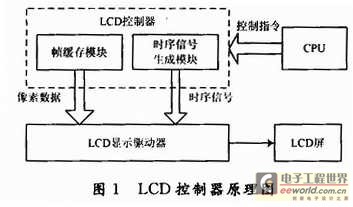

在嵌入式系统中,LCD控制器是非常重要的片上外围设备,处理器通过LCD控制器来完成对显示驱动器的控制,最终实现LCD屏的点亮操作。由于LCD显示驱动器只是一个被动系统,还需要有控制电路提供驱动系统所必须的扫描时序信号和显示数据。处理器通过对LCD控制器的操作,实现对LCD显示扫描时序的设置和显示数据的写入,从而完成对LCD的显示操作,其原理图如图1所示。

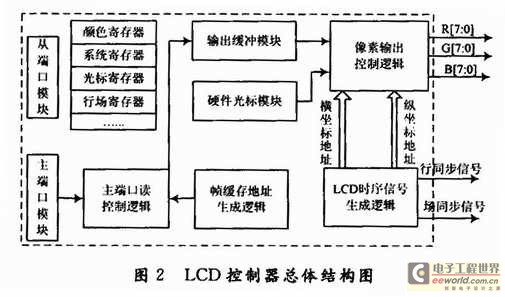

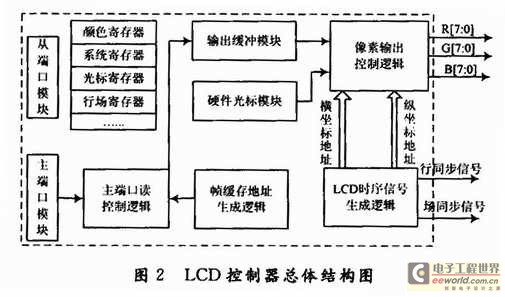

在SoPCBuilder中以自定义组件的形式对LCD控制器进行设计,该控制器组件具有Avalon总线接口,可以很容易地将其与其他标准IP核一起构建以。NiosⅡCPU为核心的片上系统。NiosⅡ处理器通过Avalon从端口对LCD控制器的寄存器组进行配置,针对设计中帧缓存读操作的特点,选择以Avalon主端口接口的形式对帧缓存中的显示数据进行主动读取,并实现IP核参数化设计,提高控制器对于其他不同规格TFT液晶屏的复用性。该控制器还包含硬件光标功能,为添加外部鼠标设备接口提供了方便。LCD控制器的具体设计思路是在SDRAM中开辟一段存储空间,用来存放屏幕图像数据,称之为帧缓存。通过设计适当的硬件逻辑来建立帧缓存与屏幕图像像素之间一一对应的关系,并配合LCD显示所需的行、场时序信号,将帧缓存中的数据不断地输给LCD,用以完成最终的显示刷新。LCD控制器总体结构如图2所示。

LCD控制器的具体工作流程为刷新周期开始时,主端口模块根据帧缓存地址生成逻辑所产生的地址完成主端口的读操作,实现帧缓存中数据的读取,并将该数据输送给输出缓冲模块。同时,时序信号生成模块依据LCD屏的时序规范生成行、场同步信号,以及与像素数据同步的相关显示点的横、纵坐标。

设计的LCD控制器包含硬件光标显示模块,所以在进行最后屏幕显示时,像素输出控制逻辑有两部分的数据来源,一部分为从帧缓存中读取的屏幕数据;另一部分为硬件光标的显示数据。最后,像素输出控制逻辑根据从端口模块中各个系统寄存器内的信息向LCD屏幕发送将要显示的图像数据。

2 硬件光标模块设计

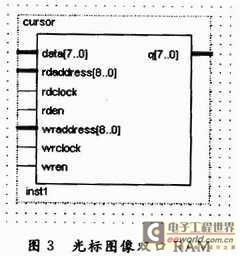

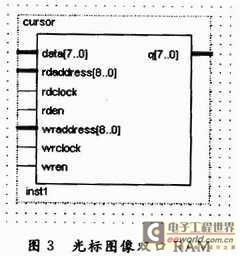

硬件光标模块为LCD控制器设计带鼠标光标的显示功能,为系统开发中添加鼠标接口提供了方便。光标显示的实现方式有硬件方式和软件方式,软件方式比较复杂,且占用大量的CPU处理时间;硬件方式用硬件逻辑资源来实现,处理速度快,不占用CPU时间。硬件方式的设计思路是为光标的图像数据设置单独的存储空间(RAM)用以保存,当LCD屏幕需要对光标进行显示时,由硬件逻辑负责在输出光标和背景图像之间做出选择。而软件部分只需简单地修改光标坐标寄存器的值,就可以完成光标在屏幕上的显示操作。采用这种方法,大大提高了系统性能。硬件光标RAM模块是通过MegWizardPlug-InManager编辑器生成的,最终生成的存储光标图像数据的双口RAM如图3所示。

3 LCD控制器组件设计

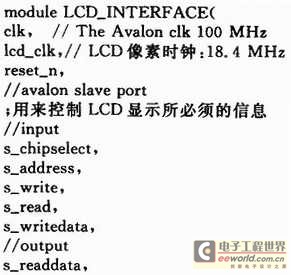

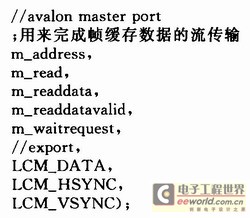

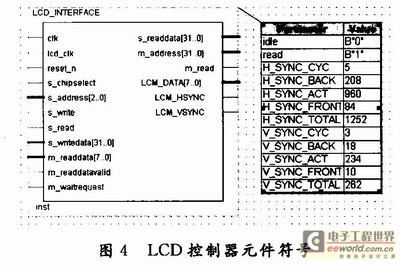

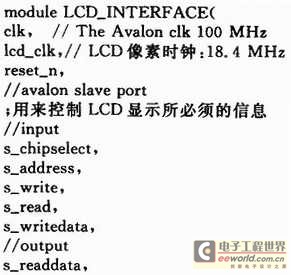

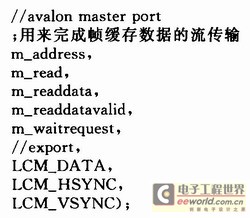

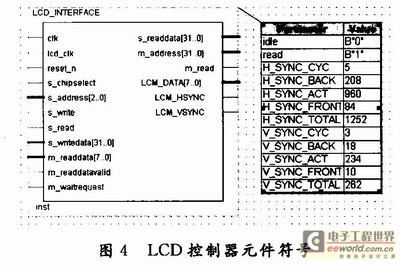

将LCD控制器按总体设计要求编写相应的硬件描述语言代码,其端口定义的程序主要有系统时钟、LCD时钟、Avalon从端口、Avalon主端口和LCD输出的定义。程序的主要内容有各种寄存器和连线的定义,行场参数的设定,行扫描状态机、场扫描状态机、Avalon主端口读控制逻辑状态机、帧缓存地址生成逻辑、LCD有效显示数据信号生成逻辑、硬件光标模块和两个例化模块的调用等。最终生成的元件符号如图4所示。

组件编辑器是SoPCBuilder的一个重要组成部分,可以使用该工具将用户定制逻辑封装成组件,并在SoPCBuilder环境中像其他标准组件一样使用。在SoPCBuilder环境下,启动组件编辑器,按照组件编辑图形用户界面的提示,做相应的操作。主要有导入硬件HDL代码LCD-INTERFACE,为硬件逻辑代码中的信号指定Avalon信号类型、Avalon接口设计和设置添加组件的界面向导等,最后就生成了用户自定义的组件

LCD_INTERFACE。它以IP核的形式存放在SoPCBuilder的组件库中供设计使用,把液晶显示控制器设计成Avalon总线的slave设备。由于该控制器是参数化的,可以很容易地修改TFT_LCD液晶的时序参数,具有很强的通用性。通过Terasic公司的TRDB_LTM彩色液晶显示开发板进行设计验证。TRDB_LTM采用Toppoly公司的TFT_LCD模块TD043MTEAl,4.3英寸屏。时序参数中,横向时序参数为:时钟频率(NCLK)33.2MHz;横向有效数据为800点;H_LINE=1056;Hsync_Blank=216;Hsync_Front_Porch=40。纵向时序参数为:纵向有效数据为480点;V_LINE=525;Vsync_Blank=35;Vsync_Front_Porch=10。

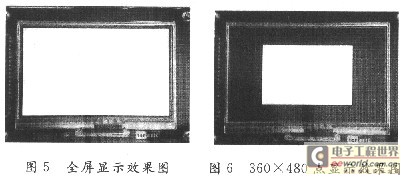

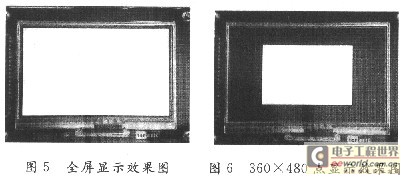

按上面的时序参数在SoPC系统中配置TFT_LCD液晶IP核后,设置屏幕背景为白屏,并在上面用黑线画一个矩形,显示结果如图5所示。如果将时序参数中的数据做如下调整,将横向有效显示数据设置为480点,纵向有效显示数据设置为360点,做同上的验证,显示结果如图6所示。由这两个图可见,该控制器具有很好的通用性。

SoPCBuilder是Altera公司实现SoPC概念的一款工具软件,使得用户可以通过自定义逻辑的方法方便地开发基于NiosⅡ的SoPC系统。So-PCBuilder集成在EDA工具QuartusⅡ中,提供NiosⅡ处理器及一些常用外设接口,用于组建一个在模块级和组件级定义的系统,能够自动生成片上总线和总线仲裁器等所需的逻辑。基于SoPC的设计在很大程度上依赖于利用集成电路IP(intellectualproperty)。集成电路IP是指经过预先设计、预先验证、符合产业界普遍认同的设计规范和设计标准,具有相对独立,并可以重复利用的电路模块或子系统。本文中提出一种基于SoPC的参数化TFT-LCD控制器IP核设计,用硬件描述语言实现控制器的逻辑功能,这种参数化的组件设计具有很强的通用性和兼容性。

1 通用册LCD控制器总体设计

在嵌入式系统中,LCD控制器是非常重要的片上外围设备,处理器通过LCD控制器来完成对显示驱动器的控制,最终实现LCD屏的点亮操作。由于LCD显示驱动器只是一个被动系统,还需要有控制电路提供驱动系统所必须的扫描时序信号和显示数据。处理器通过对LCD控制器的操作,实现对LCD显示扫描时序的设置和显示数据的写入,从而完成对LCD的显示操作,其原理图如图1所示。

在SoPCBuilder中以自定义组件的形式对LCD控制器进行设计,该控制器组件具有Avalon总线接口,可以很容易地将其与其他标准IP核一起构建以。NiosⅡCPU为核心的片上系统。NiosⅡ处理器通过Avalon从端口对LCD控制器的寄存器组进行配置,针对设计中帧缓存读操作的特点,选择以Avalon主端口接口的形式对帧缓存中的显示数据进行主动读取,并实现IP核参数化设计,提高控制器对于其他不同规格TFT液晶屏的复用性。该控制器还包含硬件光标功能,为添加外部鼠标设备接口提供了方便。LCD控制器的具体设计思路是在SDRAM中开辟一段存储空间,用来存放屏幕图像数据,称之为帧缓存。通过设计适当的硬件逻辑来建立帧缓存与屏幕图像像素之间一一对应的关系,并配合LCD显示所需的行、场时序信号,将帧缓存中的数据不断地输给LCD,用以完成最终的显示刷新。LCD控制器总体结构如图2所示。

LCD控制器的具体工作流程为刷新周期开始时,主端口模块根据帧缓存地址生成逻辑所产生的地址完成主端口的读操作,实现帧缓存中数据的读取,并将该数据输送给输出缓冲模块。同时,时序信号生成模块依据LCD屏的时序规范生成行、场同步信号,以及与像素数据同步的相关显示点的横、纵坐标。

设计的LCD控制器包含硬件光标显示模块,所以在进行最后屏幕显示时,像素输出控制逻辑有两部分的数据来源,一部分为从帧缓存中读取的屏幕数据;另一部分为硬件光标的显示数据。最后,像素输出控制逻辑根据从端口模块中各个系统寄存器内的信息向LCD屏幕发送将要显示的图像数据。

2 硬件光标模块设计

硬件光标模块为LCD控制器设计带鼠标光标的显示功能,为系统开发中添加鼠标接口提供了方便。光标显示的实现方式有硬件方式和软件方式,软件方式比较复杂,且占用大量的CPU处理时间;硬件方式用硬件逻辑资源来实现,处理速度快,不占用CPU时间。硬件方式的设计思路是为光标的图像数据设置单独的存储空间(RAM)用以保存,当LCD屏幕需要对光标进行显示时,由硬件逻辑负责在输出光标和背景图像之间做出选择。而软件部分只需简单地修改光标坐标寄存器的值,就可以完成光标在屏幕上的显示操作。采用这种方法,大大提高了系统性能。硬件光标RAM模块是通过MegWizardPlug-InManager编辑器生成的,最终生成的存储光标图像数据的双口RAM如图3所示。

3 LCD控制器组件设计

将LCD控制器按总体设计要求编写相应的硬件描述语言代码,其端口定义的程序主要有系统时钟、LCD时钟、Avalon从端口、Avalon主端口和LCD输出的定义。程序的主要内容有各种寄存器和连线的定义,行场参数的设定,行扫描状态机、场扫描状态机、Avalon主端口读控制逻辑状态机、帧缓存地址生成逻辑、LCD有效显示数据信号生成逻辑、硬件光标模块和两个例化模块的调用等。最终生成的元件符号如图4所示。

组件编辑器是SoPCBuilder的一个重要组成部分,可以使用该工具将用户定制逻辑封装成组件,并在SoPCBuilder环境中像其他标准组件一样使用。在SoPCBuilder环境下,启动组件编辑器,按照组件编辑图形用户界面的提示,做相应的操作。主要有导入硬件HDL代码LCD-INTERFACE,为硬件逻辑代码中的信号指定Avalon信号类型、Avalon接口设计和设置添加组件的界面向导等,最后就生成了用户自定义的组件

LCD_INTERFACE。它以IP核的形式存放在SoPCBuilder的组件库中供设计使用,把液晶显示控制器设计成Avalon总线的slave设备。由于该控制器是参数化的,可以很容易地修改TFT_LCD液晶的时序参数,具有很强的通用性。通过Terasic公司的TRDB_LTM彩色液晶显示开发板进行设计验证。TRDB_LTM采用Toppoly公司的TFT_LCD模块TD043MTEAl,4.3英寸屏。时序参数中,横向时序参数为:时钟频率(NCLK)33.2MHz;横向有效数据为800点;H_LINE=1056;Hsync_Blank=216;Hsync_Front_Porch=40。纵向时序参数为:纵向有效数据为480点;V_LINE=525;Vsync_Blank=35;Vsync_Front_Porch=10。

按上面的时序参数在SoPC系统中配置TFT_LCD液晶IP核后,设置屏幕背景为白屏,并在上面用黑线画一个矩形,显示结果如图5所示。如果将时序参数中的数据做如下调整,将横向有效显示数据设置为480点,纵向有效显示数据设置为360点,做同上的验证,显示结果如图6所示。由这两个图可见,该控制器具有很好的通用性。

电子 显示器 LCD 嵌入式 PCB Altera EDA Quartus 总线 集成电路 电路 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)