基于FPGA的数据采集控制模块的研究与设计

时间:11-09

来源:互联网

点击:

2.3 RAM读写控制器的设计

在该模块设计中,RAM读写控制模块又分为读控制模块、写控制模块和读写状态转换模块。写控制模块中两个输入信号分别与A/D转换控制模块的数据锁存和转换输出相连。当锁存信号使能,即发出写信号,将数据存储到外部RAM的第600个地址空间之后,再对之前的数据进行前移,以达到数据的及时更新。读控制模块的控制信号分别与写更新完毕信号和读信号相连,当写更新完毕信号使能时,只要接到读信号,则依次读完外部RAM前600个地址空间(一场)的数据。

2.4 键盘扫描控制器的设计

键盘控制模块由四个模块组成,包括:时钟分频模块、行键值输出模块、键值锁存模块和键值合成模块。键值锁存模块将按下按键的行、列信息锁存,并交由键值合成模块,该模块配合行键输出模块输出的结果进行查表,最终确定键值。

3 仿真结果

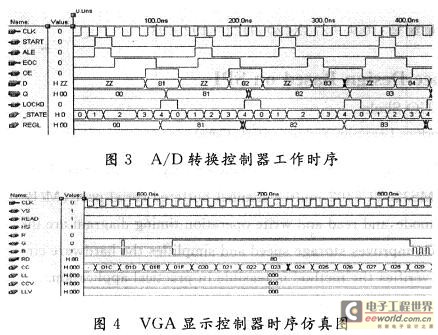

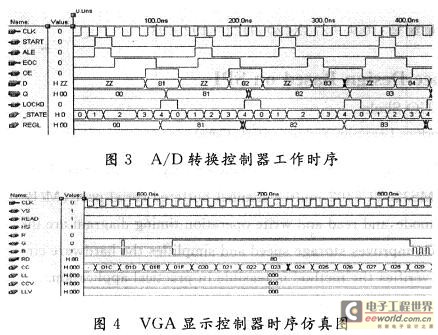

Max+PlusⅡ仿真平台的图形输入方式直观,符合传统数字系统设计人员的习惯,便于进行接口的设计,容易实现仿真,便于信号的观察。基于以上考虑,利用此平台,用硬件描述语言VHDL来实现各个功能模块,A/D转换控制器和VGA显示控制器模块的时序仿真结果如图3、图4所示。

4 结 语

这里的数据采集控制模块主要以FPGA为基础,本着软件硬件化的思路,着重研究主控制模块的实现。由于采用FPGA作为控制处理器,其速度快,效率高,且标准的VGA接口使得系统的使用更加便捷,键盘控制的多通道间切换,也为实现多路采集奠定了基础。

在该模块设计中,RAM读写控制模块又分为读控制模块、写控制模块和读写状态转换模块。写控制模块中两个输入信号分别与A/D转换控制模块的数据锁存和转换输出相连。当锁存信号使能,即发出写信号,将数据存储到外部RAM的第600个地址空间之后,再对之前的数据进行前移,以达到数据的及时更新。读控制模块的控制信号分别与写更新完毕信号和读信号相连,当写更新完毕信号使能时,只要接到读信号,则依次读完外部RAM前600个地址空间(一场)的数据。

2.4 键盘扫描控制器的设计

键盘控制模块由四个模块组成,包括:时钟分频模块、行键值输出模块、键值锁存模块和键值合成模块。键值锁存模块将按下按键的行、列信息锁存,并交由键值合成模块,该模块配合行键输出模块输出的结果进行查表,最终确定键值。

3 仿真结果

Max+PlusⅡ仿真平台的图形输入方式直观,符合传统数字系统设计人员的习惯,便于进行接口的设计,容易实现仿真,便于信号的观察。基于以上考虑,利用此平台,用硬件描述语言VHDL来实现各个功能模块,A/D转换控制器和VGA显示控制器模块的时序仿真结果如图3、图4所示。

4 结 语

这里的数据采集控制模块主要以FPGA为基础,本着软件硬件化的思路,着重研究主控制模块的实现。由于采用FPGA作为控制处理器,其速度快,效率高,且标准的VGA接口使得系统的使用更加便捷,键盘控制的多通道间切换,也为实现多路采集奠定了基础。

电子 单片机 DSP ADC 电路 集成电路 FPGA 仿真 显示器 电压 VHDL 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)