一种基于FPGA/DSP的灵巧干扰平台设计与实现

时间:11-09

来源:互联网

点击:

2.2 平台软件设计

本设计中,FPGA不仅需要与DSP协同工作,完成对侦察信号的处理,同时负责对整个平台的控制。信号处理板上与FPGA通讯的接口有:AD/DDC接口、DA/DUC接口、DSP接口、RAM(SRAM/SDRAM)接口及CPCI接口。 FPGA要实现与这些接口的通讯,并协调各接口之间的工作时序,调度各接口之间的数据流向。

基于FPGA的控制软件主要完成以下功能:

(1)程序加载

程序加载分为FPGA的程序加载和DSP的程序加载。FPGA的程序加载是指通过PCI总线来给FPGA加载程序。其加载路径为:上位机→PCI总线 →FP-GA。DSP的程序加载是指通过HPI来给DSP加载信号处理程序。其加载路径为:上位机→PCI总线→FP-GA→HPI口→DSP。

(2)ADC(DDC)数据采集与存储

此过程是指FPGA把ADC(DDC)数据采集并保存在外部存储器(SDRAM或SRAM)中以备FPGA和DSP处理的过程。其数据流路径为:外部数据源→ADC→DDC(只进行ADC时DDC省略)→FPGA→SDRAM或SRAM。

(3)数据的DMA操作

DMA用于实现上位机对外部存储器(SDRAM或SRAM)的数据读写功能。DMA读的数据流路径是:外部存储器→FPGA→DMA→上位机→二进制文件。DMA发的数据流路径是:上位机→DMA→FPGA→SDRAM。

(4)配置DDC和DUC

此过程是把DDC和DUC配置文件通过FPGA配置到AD6636和GC5016中。其配置路径为:上位机→PCI总线→FPGA→DDC或DUC。

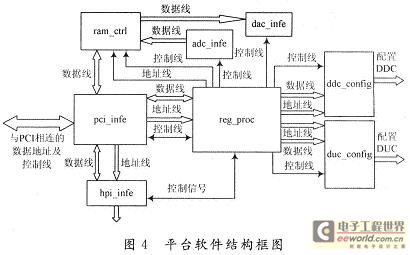

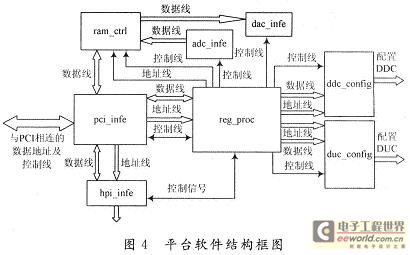

软件设计采用Verilog硬件描述语言和模块化设计,结构如图4所示。

图4中,reg_proc模块是软件控制的核心部分。通过定义内部寄存器接收上位机的控制字,给各模块发出控制信息;pci_infe是FPGA与PCI 总线的接口模块,实现平台与上位机的信号交互;FPGA通过HPI口对DSP的程序加载,由hpi_infe模块实现;adc_infe和DAC infe实现数据的A/D输入和D/A输出功能;ddc_config和duc_config完成对DDC及DUC芯片的配置;ram_ctrl模块实现 FPGA对存储器的读写功能,包括SRAM和SDRAM的子模块程序。此外,程序还设计了时钟管理模块clk_manage,用于产生全局时钟及复位信号。

3 试验验证

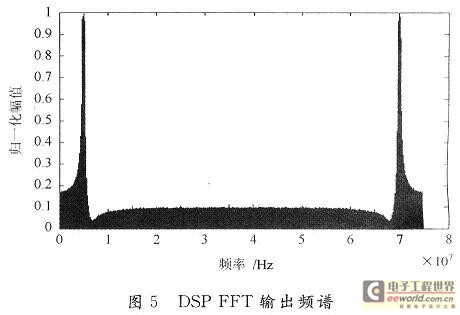

为了验证平台能否在程序控制下正确工作,本文编写了工作于DSP的8 192点FFT验证程序,实现对输入信号的FFT变换。

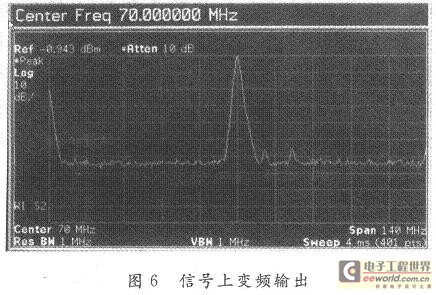

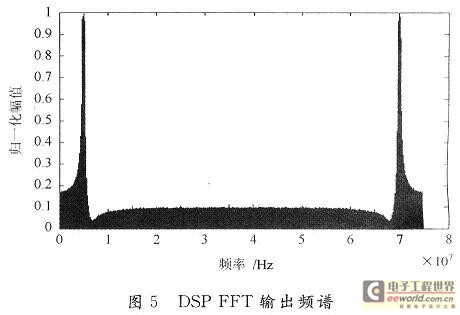

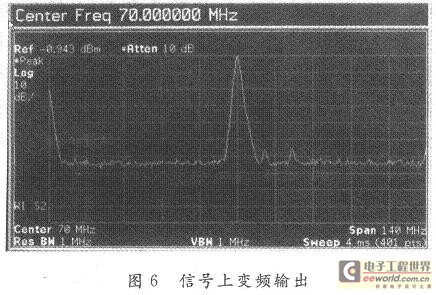

试验中设置DDC为70 MHz混频,DUC 70 MHz中频输出,输入信号为75 MHz正弦波。在FPGA/DSP程序加载和DDC/DUC配置完成后,首先进行ADC数据采集,把采集得到的数据存储到SRAM中,DSP与SRAM进行数据交互并在DSP中完成8 192点的FFT运算,计算结果保存于SDRAM中,经DMA方式读取到上位机硬盘形成二进制文件。同时将混频后的5 MHz单频信号从SRAM读出上变频到70 MHz输出。试验结果如图5、图6所示。

由图5可知,DMA输出的FFT结果显示处理的下变频信号为5 MHz,等于预期值;图6显示5 MHz单频信号经上变频后输出为70 MHz中频模拟信号。试验证明,平台的软硬件均能正确工作,实现了设计目的。

4 结 语

根据灵巧干扰平台功能要求,设计了基于FPGA/DSP的硬件平台,采用Verilog HDL及模块化方法设计了硬件平台的控制软件。试验结果表明,灵巧干扰平台构成合理,硬件设计、软件设计可靠,满足了灵巧干扰平台的功能要求,为灵巧干扰技术研究提供了硬件平台支持,该平台已成功应用于工程项目。

本设计中,FPGA不仅需要与DSP协同工作,完成对侦察信号的处理,同时负责对整个平台的控制。信号处理板上与FPGA通讯的接口有:AD/DDC接口、DA/DUC接口、DSP接口、RAM(SRAM/SDRAM)接口及CPCI接口。 FPGA要实现与这些接口的通讯,并协调各接口之间的工作时序,调度各接口之间的数据流向。

基于FPGA的控制软件主要完成以下功能:

(1)程序加载

程序加载分为FPGA的程序加载和DSP的程序加载。FPGA的程序加载是指通过PCI总线来给FPGA加载程序。其加载路径为:上位机→PCI总线 →FP-GA。DSP的程序加载是指通过HPI来给DSP加载信号处理程序。其加载路径为:上位机→PCI总线→FP-GA→HPI口→DSP。

(2)ADC(DDC)数据采集与存储

此过程是指FPGA把ADC(DDC)数据采集并保存在外部存储器(SDRAM或SRAM)中以备FPGA和DSP处理的过程。其数据流路径为:外部数据源→ADC→DDC(只进行ADC时DDC省略)→FPGA→SDRAM或SRAM。

(3)数据的DMA操作

DMA用于实现上位机对外部存储器(SDRAM或SRAM)的数据读写功能。DMA读的数据流路径是:外部存储器→FPGA→DMA→上位机→二进制文件。DMA发的数据流路径是:上位机→DMA→FPGA→SDRAM。

(4)配置DDC和DUC

此过程是把DDC和DUC配置文件通过FPGA配置到AD6636和GC5016中。其配置路径为:上位机→PCI总线→FPGA→DDC或DUC。

软件设计采用Verilog硬件描述语言和模块化设计,结构如图4所示。

图4中,reg_proc模块是软件控制的核心部分。通过定义内部寄存器接收上位机的控制字,给各模块发出控制信息;pci_infe是FPGA与PCI 总线的接口模块,实现平台与上位机的信号交互;FPGA通过HPI口对DSP的程序加载,由hpi_infe模块实现;adc_infe和DAC infe实现数据的A/D输入和D/A输出功能;ddc_config和duc_config完成对DDC及DUC芯片的配置;ram_ctrl模块实现 FPGA对存储器的读写功能,包括SRAM和SDRAM的子模块程序。此外,程序还设计了时钟管理模块clk_manage,用于产生全局时钟及复位信号。

3 试验验证

为了验证平台能否在程序控制下正确工作,本文编写了工作于DSP的8 192点FFT验证程序,实现对输入信号的FFT变换。

试验中设置DDC为70 MHz混频,DUC 70 MHz中频输出,输入信号为75 MHz正弦波。在FPGA/DSP程序加载和DDC/DUC配置完成后,首先进行ADC数据采集,把采集得到的数据存储到SRAM中,DSP与SRAM进行数据交互并在DSP中完成8 192点的FFT运算,计算结果保存于SDRAM中,经DMA方式读取到上位机硬盘形成二进制文件。同时将混频后的5 MHz单频信号从SRAM读出上变频到70 MHz输出。试验结果如图5、图6所示。

由图5可知,DMA输出的FFT结果显示处理的下变频信号为5 MHz,等于预期值;图6显示5 MHz单频信号经上变频后输出为70 MHz中频模拟信号。试验证明,平台的软硬件均能正确工作,实现了设计目的。

4 结 语

根据灵巧干扰平台功能要求,设计了基于FPGA/DSP的硬件平台,采用Verilog HDL及模块化方法设计了硬件平台的控制软件。试验结果表明,灵巧干扰平台构成合理,硬件设计、软件设计可靠,满足了灵巧干扰平台的功能要求,为灵巧干扰技术研究提供了硬件平台支持,该平台已成功应用于工程项目。

射频 ADC DSP FPGA 总线 CPLD DAC Xilinx Verilog 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- CPLD在射频卡读写器中的应用(08-02)

- FPGA实现安全可靠的蓝牙通信(09-20)

- 用FPGA设计软件无线电和调制解调器(09-21)

- 可编程逻辑器件接地设计(09-30)

- 用低成本FPGA实现低延迟变化的CPRI(10-17)