基于PC104总线的2FSK调制器的设计与实现

时间:11-09

来源:互联网

点击:

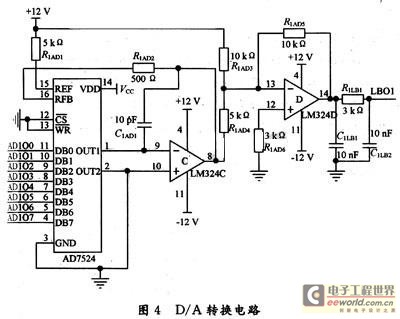

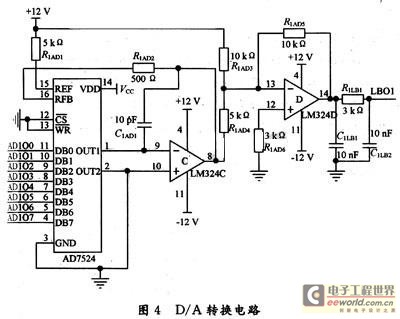

4 D/A转换电路

D/A转换共包括四路,其主要功能是将FPGA输出的已调制好的2FSK数字信号转换为正弦波信号。由于FPGA在进行数字调制时产生的是连续量化的正弦波形,两个频率之间不存在相位的突变,不会存在大量的高频杂波,因此,后期的信号处理电路使用放大电路与简单的π型滤波器对信号进行处理即可得到比较理想的2FSK信号。

D/A转换电路如图4所示。

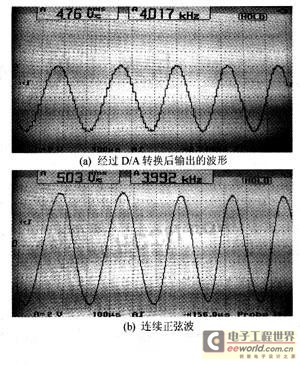

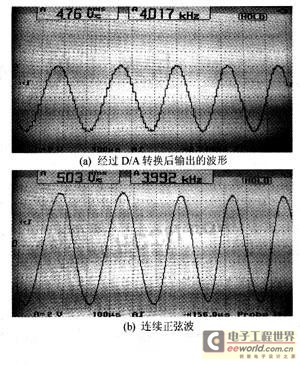

此电路采用AD7524作为D/A转换器,AD7524属于T型电阻网络型DAC,电流输出,8位数字输入,输出建立时间0.2μs/0.15μs,其数字输入端可采用5 V/15 V两种输入,本电路采用兼容TTL电平的5 V输入。电路中将其输入控制端CS、WR同时接地,当有来自FPGA的数据AD101~7输入时无需锁存,直接进行转换,因此要求FPGA的输出要具有锁存功能,此接法可减少输出控制线,减少时序干扰。R1AD1和R1AD2为D/A输出波形调整电阻,主要用于调整波形位置,不致产生失真。D/A输出采用双极性接法,通过两路LM324通用放大器进行电压放大,输出2FSK信号。图5(a)为经过D/A转换后输出的波形在示波器上的截图,由图中可以看到,数字调制并经D/A转换后,波形是一种阶梯状正弦波,且波形连续,频率变换交界处无相位突变。该信号经过双极性放大器放大并通过π型滤波器后变成如图5(b)所示的连续正弦波。

图5 2FSK信号滤波前后波形比较

5 结语

采用FPGA进行2FSK调制不但能产生连续相位,还能通过软件直接修改其调制方式、产生频率等一系列参数,具有很好的通用性。

本电路中数据提取电路属于原理性电路,实际设计中可将该部分电路置于FPGA内部进行设计,而系统参考时钟SYSCLK可接在FPGA的全局时钟输入端,减少延迟差异。

D/A转换共包括四路,其主要功能是将FPGA输出的已调制好的2FSK数字信号转换为正弦波信号。由于FPGA在进行数字调制时产生的是连续量化的正弦波形,两个频率之间不存在相位的突变,不会存在大量的高频杂波,因此,后期的信号处理电路使用放大电路与简单的π型滤波器对信号进行处理即可得到比较理想的2FSK信号。

D/A转换电路如图4所示。

此电路采用AD7524作为D/A转换器,AD7524属于T型电阻网络型DAC,电流输出,8位数字输入,输出建立时间0.2μs/0.15μs,其数字输入端可采用5 V/15 V两种输入,本电路采用兼容TTL电平的5 V输入。电路中将其输入控制端CS、WR同时接地,当有来自FPGA的数据AD101~7输入时无需锁存,直接进行转换,因此要求FPGA的输出要具有锁存功能,此接法可减少输出控制线,减少时序干扰。R1AD1和R1AD2为D/A输出波形调整电阻,主要用于调整波形位置,不致产生失真。D/A输出采用双极性接法,通过两路LM324通用放大器进行电压放大,输出2FSK信号。图5(a)为经过D/A转换后输出的波形在示波器上的截图,由图中可以看到,数字调制并经D/A转换后,波形是一种阶梯状正弦波,且波形连续,频率变换交界处无相位突变。该信号经过双极性放大器放大并通过π型滤波器后变成如图5(b)所示的连续正弦波。

图5 2FSK信号滤波前后波形比较

5 结语

采用FPGA进行2FSK调制不但能产生连续相位,还能通过软件直接修改其调制方式、产生频率等一系列参数,具有很好的通用性。

本电路中数据提取电路属于原理性电路,实际设计中可将该部分电路置于FPGA内部进行设计,而系统参考时钟SYSCLK可接在FPGA的全局时钟输入端,减少延迟差异。

嵌入式 总线 电路 FPGA Altera Quartus VHDL 滤波器 电阻 DAC 电流 放大器 电压 示波器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)