基于Nios Ⅱ软核系统的电能质量监测系统设计

时间:11-09

来源:互联网

点击:

3 电能质量检测系统软件设计

3.1 SoPC Builder设计

对应系统的硬件平台结构,添加NiosⅡProcessor,选择其为快速型,以确保系统的速度性能。再添加SPI,PIO,Character LCD,FLASH Memory,Avalon Tristate Bridge,SDRAM Controller,On chip Memory,DSP,timer这些模块。设置好模块的各项参数后,点击System控件里的两个选项为各模块主动分配地址和中断。然后在NiosⅡMore“CPU”Setting里选Reset Address为FLASH,选Exception AddFess为SDR-AM。最后点击Generate生成对应的ptf文件。这样系统的SoPC Bui[der设计基本完成。

3.2 NiosⅡIDE设计

进入NiosⅡIDE后新建一个应用工程,选择ptf文件和Black Project,这样一个基于已有SoPC的空白应用工程建立完毕。然后在System Library里进行必要工程设置。接着将电能参数算法的C程序填入工程里,再进行软件的编译调试等。调试完毕后,一并将所有程序与可执行文件全下载到FPGA上。至此,一个基于NiosⅡ的电能质量监测SoPC设计完成。

4 结果分析

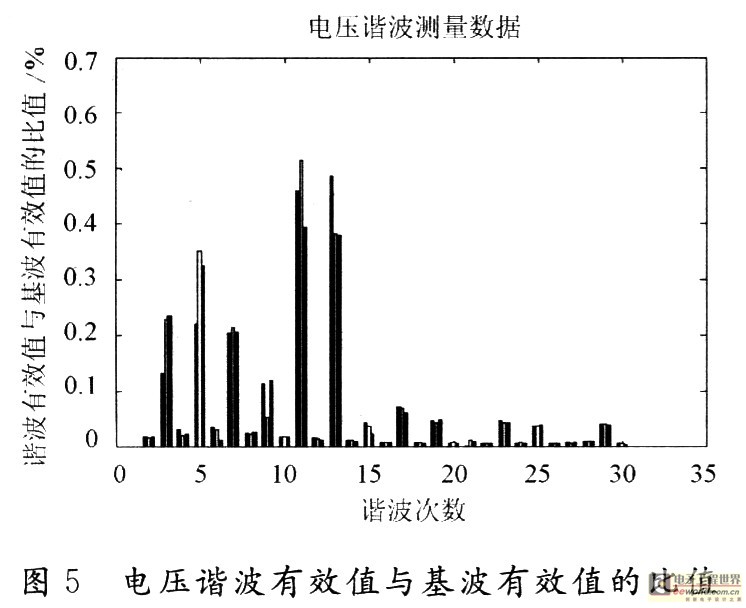

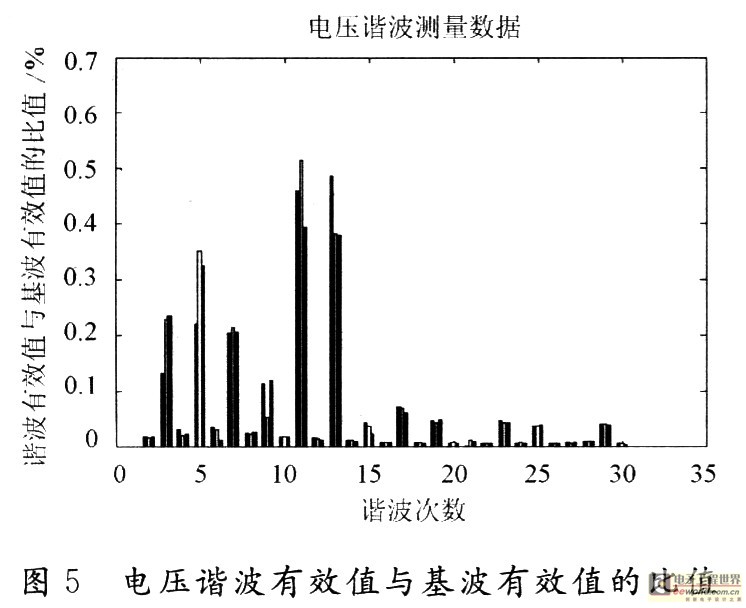

电能质量检测结果主要包括电流、电压的谐波分析数据、电功率测量值数据、供电电压的测量数据、频率的测量数据、三相不平衡度的测量数据、闪变的测量数据以及误差分析等。从实测数据中可以看出,由于各种非线性电力电子装置的广泛使用,增加了高次谐波的含有量,现以三相电压的谐波分析数据为例,得到第2~30次谐波的谐波含有率,即第n次谐波有效值与基波有效值的比值,如柱状图5所示。

图5中,连续的三根柱子分别代表A相、B相、C相的电压谐波含有率。可以看出,奇数次谐波的谐波含有率明显比偶数次谐波含有率高,其中以第3,5,7,9,1l,13谐波含量最为明显,且A,B,C三相电压相应的谐波含有率差不多,除了B相的第9次和第13次谐波含有率比A相,C相略高一些。应该尽可能地降低谐波含有量,比如从电源电压、线路阻抗、负荷特性等方面着手,降低高次谐波含有量。

本文提出一种基于NiosⅡ的电能质量监测系统的设计方案,可以实现对电能信号的采集、处理、存储与显示等功能,达到实时系统的要求。但由于经验及技术有限,该系统在某些方面还有待提高。譬如如何进一步减小三相不平衡度、闪变的危害等。本系统利用了可配置的优势,有兴趣的朋友可以在此基础上根据自己的具体需求来进行相应的填充、修改、完善,得到更优秀的电能质量监测SoPC。

3.1 SoPC Builder设计

对应系统的硬件平台结构,添加NiosⅡProcessor,选择其为快速型,以确保系统的速度性能。再添加SPI,PIO,Character LCD,FLASH Memory,Avalon Tristate Bridge,SDRAM Controller,On chip Memory,DSP,timer这些模块。设置好模块的各项参数后,点击System控件里的两个选项为各模块主动分配地址和中断。然后在NiosⅡMore“CPU”Setting里选Reset Address为FLASH,选Exception AddFess为SDR-AM。最后点击Generate生成对应的ptf文件。这样系统的SoPC Bui[der设计基本完成。

3.2 NiosⅡIDE设计

进入NiosⅡIDE后新建一个应用工程,选择ptf文件和Black Project,这样一个基于已有SoPC的空白应用工程建立完毕。然后在System Library里进行必要工程设置。接着将电能参数算法的C程序填入工程里,再进行软件的编译调试等。调试完毕后,一并将所有程序与可执行文件全下载到FPGA上。至此,一个基于NiosⅡ的电能质量监测SoPC设计完成。

4 结果分析

电能质量检测结果主要包括电流、电压的谐波分析数据、电功率测量值数据、供电电压的测量数据、频率的测量数据、三相不平衡度的测量数据、闪变的测量数据以及误差分析等。从实测数据中可以看出,由于各种非线性电力电子装置的广泛使用,增加了高次谐波的含有量,现以三相电压的谐波分析数据为例,得到第2~30次谐波的谐波含有率,即第n次谐波有效值与基波有效值的比值,如柱状图5所示。

图5中,连续的三根柱子分别代表A相、B相、C相的电压谐波含有率。可以看出,奇数次谐波的谐波含有率明显比偶数次谐波含有率高,其中以第3,5,7,9,1l,13谐波含量最为明显,且A,B,C三相电压相应的谐波含有率差不多,除了B相的第9次和第13次谐波含有率比A相,C相略高一些。应该尽可能地降低谐波含有量,比如从电源电压、线路阻抗、负荷特性等方面着手,降低高次谐波含有量。

本文提出一种基于NiosⅡ的电能质量监测系统的设计方案,可以实现对电能信号的采集、处理、存储与显示等功能,达到实时系统的要求。但由于经验及技术有限,该系统在某些方面还有待提高。譬如如何进一步减小三相不平衡度、闪变的危害等。本系统利用了可配置的优势,有兴趣的朋友可以在此基础上根据自己的具体需求来进行相应的填充、修改、完善,得到更优秀的电能质量监测SoPC。

DSP FPGA 电压 电流 嵌入式 总线 LCD 电力电子 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- FPGA作为协处理器在实时系统中的应用(04-08)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)

- 基于Spartan-3A DSP的安全视频分析(05-01)