一种基于FPGA的NoC验证平台的构建

时间:11-09

来源:互联网

点击:

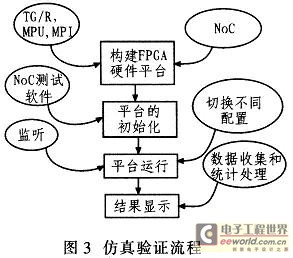

2 仿真验证流程

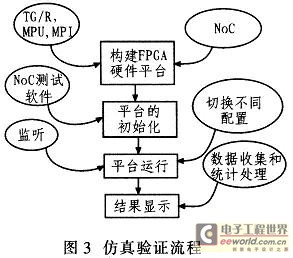

该验证平台的验证流程包括FPGA硬件平台的构建和对该硬件平台的初始化配置以及NoC运行之后的信息收集和统计处理。仿真验证流程如图3所示。

其流程简述如下:1)根据硬件架构思想和模块化设计策略将用HDL语言描述的NoC连接到FPGA硬件平台;2)初始化配置FPGA硬件平台,在PC机上编写NoC测试软件,并通过Jtag线下载到MPU上运行,配置TG产生指定流量,并注入到NoC中;3)当FPGA平台运行时,即当数据在NoC各个交换节点之间传送或停止传送时,用户可以随时改变配置以产生不同的流量,来测试NoC在不同流量下的性能,并随时监听测试平台的运行情况;4)将TR收集到的数据在NiosⅡIDE的控制台显示,并保存数据。然后对收集到的数据进行统计处理,并以图形的方式直观显示待测NoC的性能。

3 NoC性能统计处理

在验证平台中,采用PC机对NoC中运行之后相关的数据进行处理,并借助于第三方工具将处理结果以图形方式显示,以直观表示NoC的性能。该平台对于课题组设计的Mesh结构的NoC进行了功能验证和性能评估。

主要处理包括平均网络吞吐量和最近收到的80个数据包从发送端到接收端的网络平均延时以及误码统计,下面简单介绍性能评估的方法:

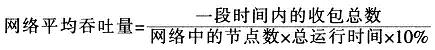

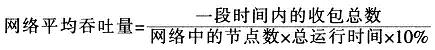

1)网络平均吞吐量 对于TR收集到的收包个数通过PC读取之后,绘制性能曲线图。以归一化仿真时间为基准,以相同时间段中收集的数据包数目作为网络总吞吐量。

式中,总运行时间xlO%表示取归一化时延的l/l0。

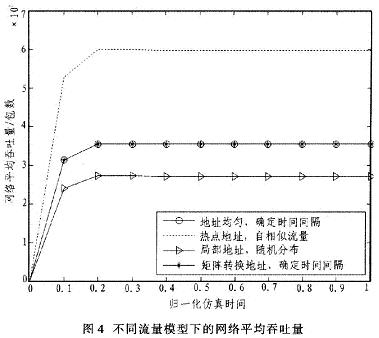

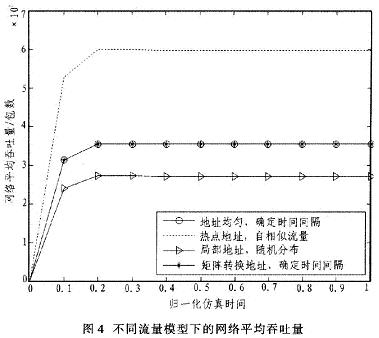

图4给出了在不同流量模型下,每包4个数据片时,所设计NoC的网络平均吞吐量。

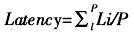

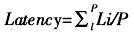

2)平均网络延迟 对于TR收集到的最近80个数据包从发送端到接收端的延迟信息,以归一化仿真时间为基准,计算平均网络延迟:

式中,P是发包总数,每个包的延迟为Li,那么Latency就是一段时间内的平均网络延迟。

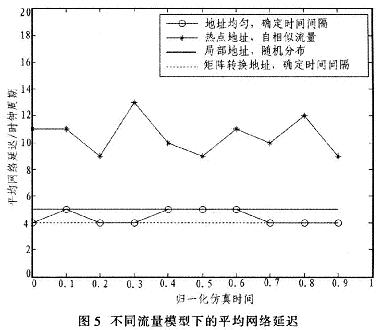

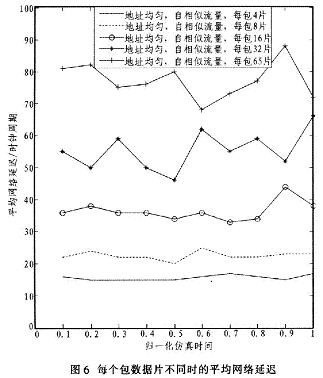

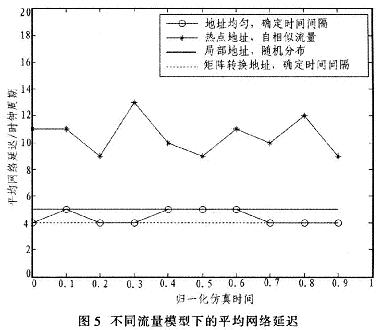

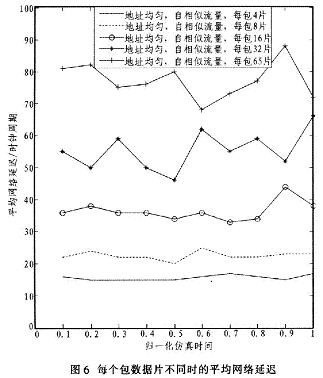

图5给出了在不同流量模型下,在相同仿真时间段中接收到的数据包的平均网络延迟。图6给出了在相同的流量模型-均匀地址,自相似流量模型下,在相同仿真时间段中,对于每包分片不同时的平均网络延迟。

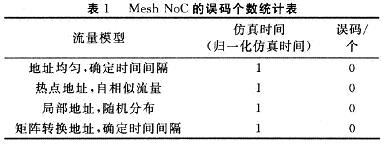

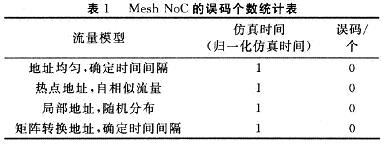

3)误码统计 表l给出了误码个数统计表,这里所设计的NoC是有保障服务,因此,在NoC运行过程中并不产生误码。验证结果与实际设计相一致。

4 结束语

本文提出了一种基于FPGA的NoC验证平台。详细讨论了该验证平台中FPGA硬件平台和NoC软件的基本功能,并阐述了TG/R,MPU,MPI以及NoC软件的可重用性等特点。通过一个实例仿真验证的结果说明了该验证平台的基本功能和优越性。目前正在开发不同参数化的流量模型,以便将该平台用于对各种不同NoC的验证。

该验证平台的验证流程包括FPGA硬件平台的构建和对该硬件平台的初始化配置以及NoC运行之后的信息收集和统计处理。仿真验证流程如图3所示。

其流程简述如下:1)根据硬件架构思想和模块化设计策略将用HDL语言描述的NoC连接到FPGA硬件平台;2)初始化配置FPGA硬件平台,在PC机上编写NoC测试软件,并通过Jtag线下载到MPU上运行,配置TG产生指定流量,并注入到NoC中;3)当FPGA平台运行时,即当数据在NoC各个交换节点之间传送或停止传送时,用户可以随时改变配置以产生不同的流量,来测试NoC在不同流量下的性能,并随时监听测试平台的运行情况;4)将TR收集到的数据在NiosⅡIDE的控制台显示,并保存数据。然后对收集到的数据进行统计处理,并以图形的方式直观显示待测NoC的性能。

3 NoC性能统计处理

在验证平台中,采用PC机对NoC中运行之后相关的数据进行处理,并借助于第三方工具将处理结果以图形方式显示,以直观表示NoC的性能。该平台对于课题组设计的Mesh结构的NoC进行了功能验证和性能评估。

主要处理包括平均网络吞吐量和最近收到的80个数据包从发送端到接收端的网络平均延时以及误码统计,下面简单介绍性能评估的方法:

1)网络平均吞吐量 对于TR收集到的收包个数通过PC读取之后,绘制性能曲线图。以归一化仿真时间为基准,以相同时间段中收集的数据包数目作为网络总吞吐量。

式中,总运行时间xlO%表示取归一化时延的l/l0。

图4给出了在不同流量模型下,每包4个数据片时,所设计NoC的网络平均吞吐量。

2)平均网络延迟 对于TR收集到的最近80个数据包从发送端到接收端的延迟信息,以归一化仿真时间为基准,计算平均网络延迟:

式中,P是发包总数,每个包的延迟为Li,那么Latency就是一段时间内的平均网络延迟。

图5给出了在不同流量模型下,在相同仿真时间段中接收到的数据包的平均网络延迟。图6给出了在相同的流量模型-均匀地址,自相似流量模型下,在相同仿真时间段中,对于每包分片不同时的平均网络延迟。

3)误码统计 表l给出了误码个数统计表,这里所设计的NoC是有保障服务,因此,在NoC运行过程中并不产生误码。验证结果与实际设计相一致。

4 结束语

本文提出了一种基于FPGA的NoC验证平台。详细讨论了该验证平台中FPGA硬件平台和NoC软件的基本功能,并阐述了TG/R,MPU,MPI以及NoC软件的可重用性等特点。通过一个实例仿真验证的结果说明了该验证平台的基本功能和优越性。目前正在开发不同参数化的流量模型,以便将该平台用于对各种不同NoC的验证。

半导体 总线 SoC 仿真 FPGA 电路 Quartus 嵌入式 C语言 相关文章:

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA 上同步开关噪声的分析(04-05)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)