CPLD在双轴位置检测系统中的应用设计

时间:11-08

来源:互联网

点击:

1 引言

数控机床的加T精度主要南位置检测系统的精度决定,位置检测系统一般包括传感器(旋转变压器,光电编码器,光栅)、四倍频鉴相电路、计数电路等,系统通过这些检测电机的位移和速度,发出反馈信号,从而构成闭环或半闭环控制。形成差值控制电机,进而提高机床加工精度。数控机床位置检测系统采用模块化和开放式控制,可减少电路规模和提高数控机床的加工精度,形成高密度、高精度的数控机床。采用数字电路的传统位置检测系统面积庞大、精度不高、发应速度慢,而采用CPLD器件代替数字电路正好弥补这些缺陷。

2 CPLD简介和器件选型

利用可编程逻辑器件CPLD(Complex Programable Logic Device)设计硬件系统非常方便。工程师通过传统的原理图输入法,或是硬件描述语言自由设计数字系统。通过软件仿真验证事先设计的正确性。在PCB完成后,还可利用CPLD在线修改能力,随时修改设计而不必改动硬件电路。因此,使用CPLD可大大加快硬件电路设计进程,减少PCB面积,提高系统可靠性。

根据所需逻辑门数量以及将与其连接的电路引脚数,选用ALTERA公司的EPM570T144C5型CPLD,该器件采用TQFP144封装,内部有570个逻辑单元,相当于440个宏单元,而此前常用的EPM7128只有128个宏单元。

EPM570T144C5内部有2个I/O分区,共116个通用I/O,引脚延时为8.8 ns,满足位置检测系统所需的90多个通用I/O和延时不超过10 ns的设计要求。

3 位置检测系统组成

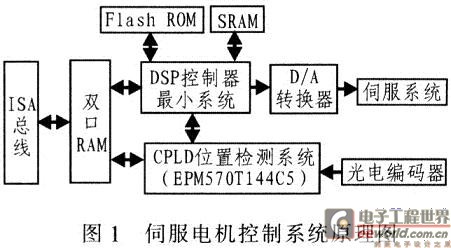

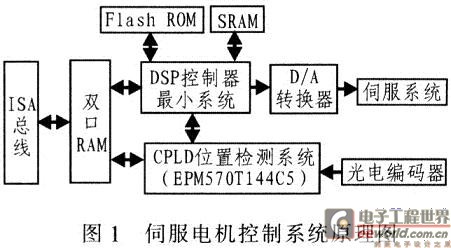

在介绍位置检测系统前,先简要介绍伺服电机控制系统(图1)。CPLD先对伺服电机光电编码器上发出的反馈信号进行译码、四倍频鉴相计数,然后将计数值存入锁存器,当用于电机控制的DSP控制器对CPLD进行读操作时,CPLD将锁存器里的计数值通过三态门输出给DSP控制器,由其控制电机的位移和速度。

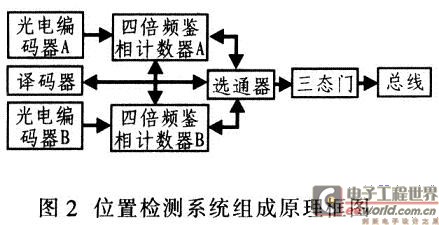

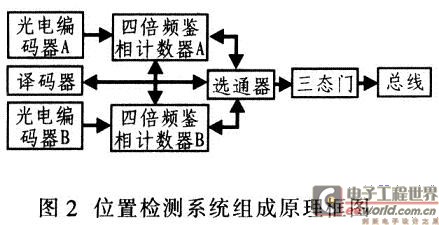

位置检测系统采用CPLD器件实现硬件电路功能,用VHDL语言编程实现译码器、四倍频鉴相计数器、选通器等模块。图2为位置检测系统组成原理图。图2 中,光电编码器A和四倍频鉴相计数器A(光电编码器B和四倍频鉴相计数器B)构成单轴计数电路,将两个单轴计数电路配合译码器、选通器则构成双轴计数电路,就是用译码器控制选通器,以选通两个计数器的计数结果并传输到总线.总线和选通器之间增加三态门进行控制。这样就实现双轴位置检测。

4 系统设计

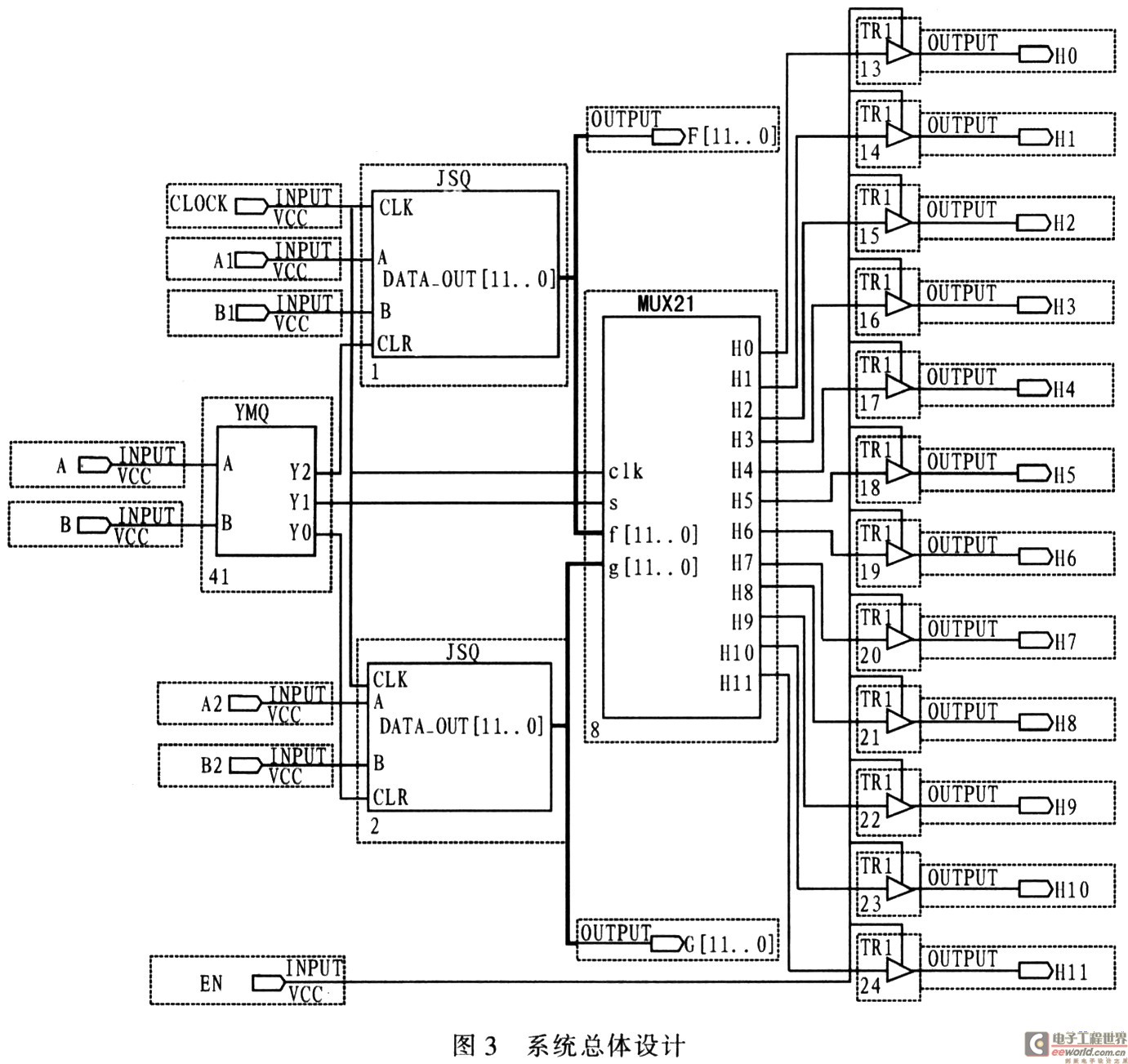

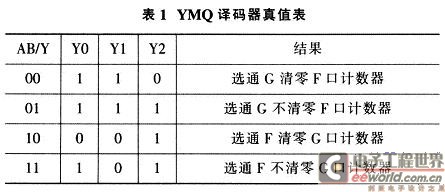

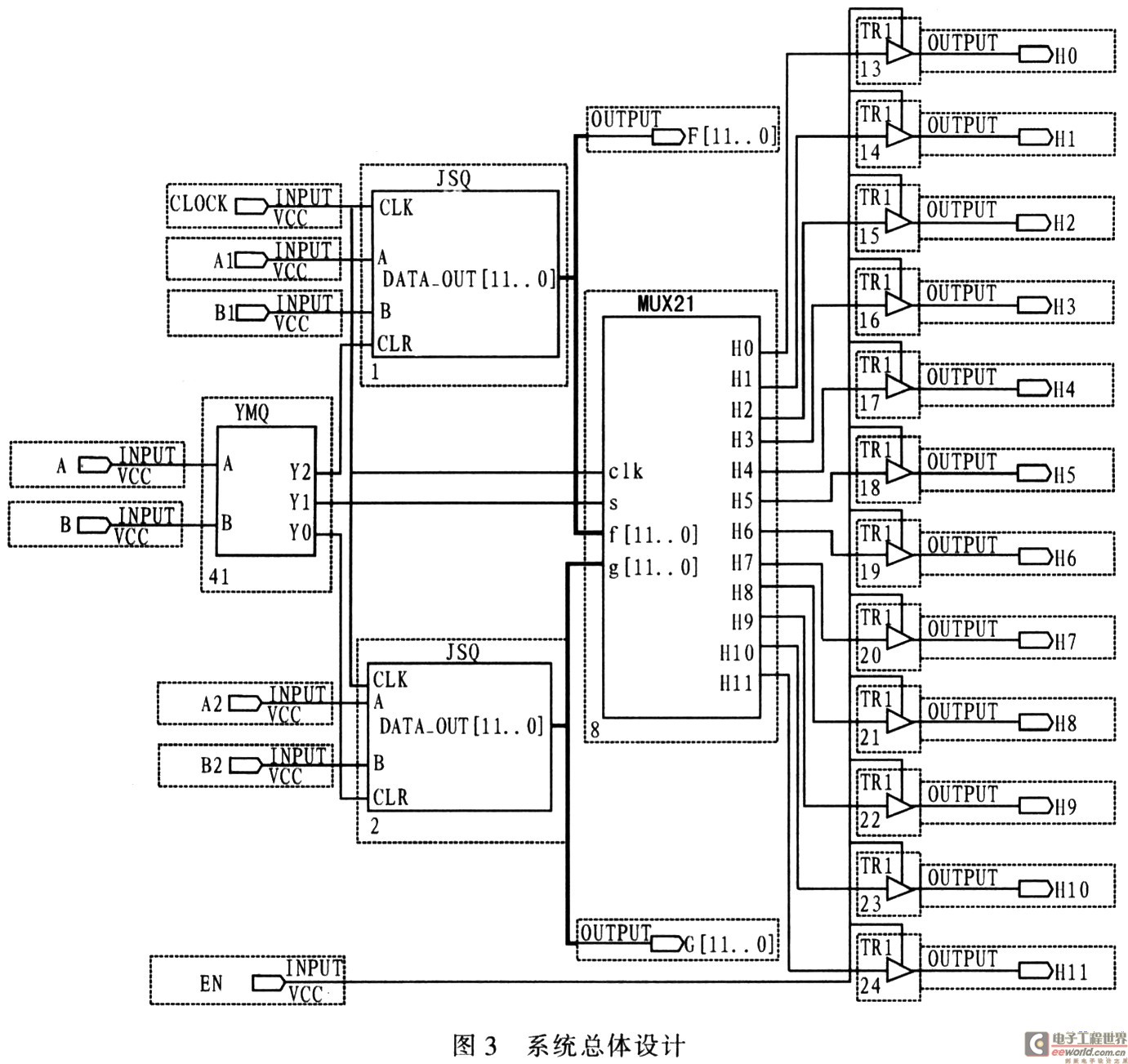

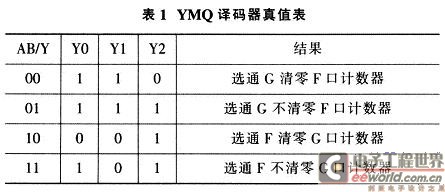

该系统设计的主要部分为伺服电机控制系统中的位置检测系统。在Ouartus II开发环境下设计系统,系统设计包括四倍频鉴相计数器、二四译码器和选通器的VHDL程序设计,如图3所示。通过图2所示的原理框图,将该系统设计的各个模块组合起来形成顶层文件,构成双轴的检测系统。图3中YMO模块为译码电路,用来选通哪轴输出,Y0、Y2用来控制计数器的清零与计数,Y1控制选通器选通,译码器真值表如表1所示。

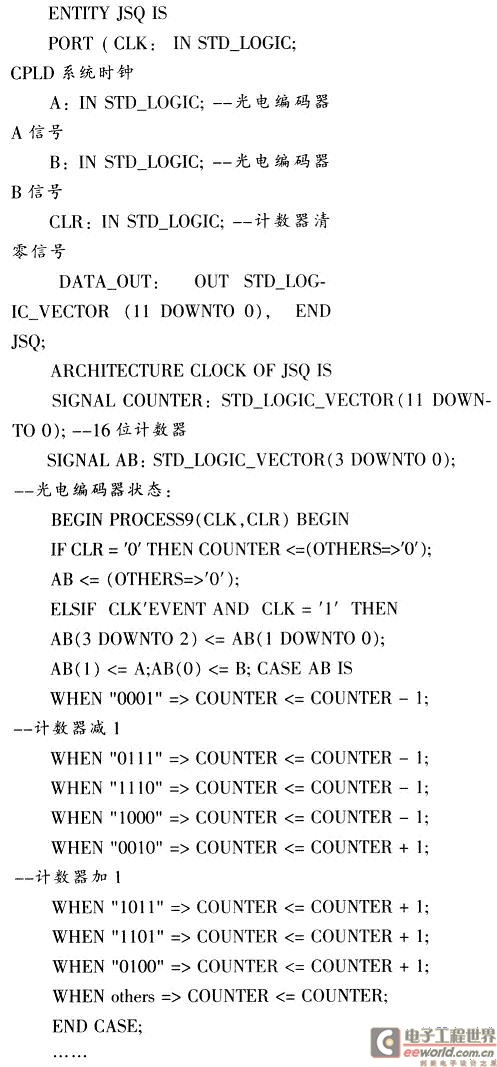

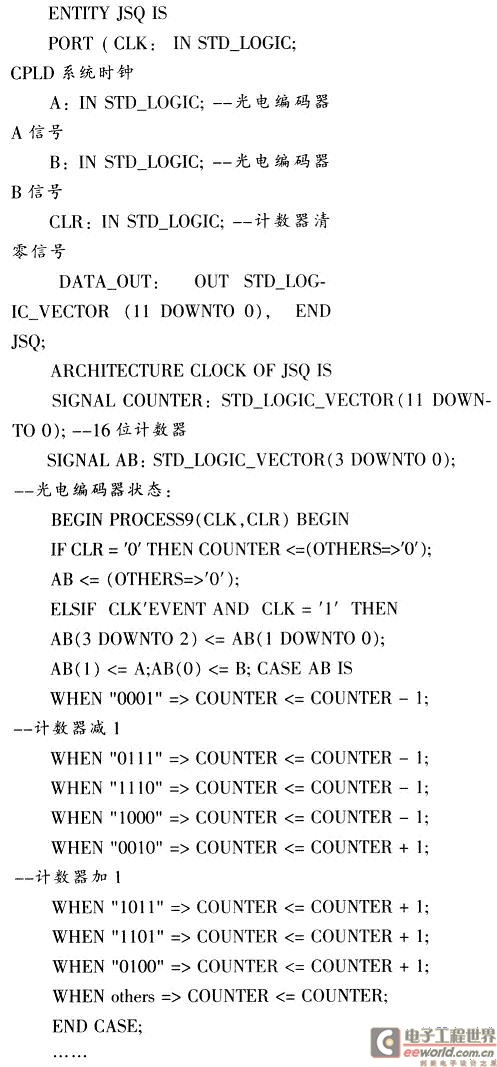

四倍频鉴相计数器的VHDL程序代码如下:

5 系统仿真

图4为系统仿真结果。当译码器控制信号AB=00时,可看出 A1超前B1,所以轴1正转;B2超前A2所以轴2反转。

三态门使能信号EN=1时,数据选择器选通G口所对应的汁数器,即轴2,清零F口对应计数器,即对轴1清零。并将计数结果传输到总线,输出信号H从FFF 变化到FF8表明轴2反转,因此汁数器逆向计数。同时在AB译码器控制信号改变时和轴1,轴2正反转的其他情况时,仿真结果均正确,满足双轴位置检测系统设计。

6 结束语

在现代数控系统中,采用 CPLD实现位置检测系统已成为主流。新一代CPLD产品MAX II EPM570以面积小、集成度高和 GPIO口多等特点使得电路板集成度和抗干扰性都得以提高,方便结合DSP控制伺服电机位臀。总之,CPLD器件的发展使得逻辑电子电路的设计更灵活、方便。它将推动数控机床甚至工业各领域的发展。

数控机床的加T精度主要南位置检测系统的精度决定,位置检测系统一般包括传感器(旋转变压器,光电编码器,光栅)、四倍频鉴相电路、计数电路等,系统通过这些检测电机的位移和速度,发出反馈信号,从而构成闭环或半闭环控制。形成差值控制电机,进而提高机床加工精度。数控机床位置检测系统采用模块化和开放式控制,可减少电路规模和提高数控机床的加工精度,形成高密度、高精度的数控机床。采用数字电路的传统位置检测系统面积庞大、精度不高、发应速度慢,而采用CPLD器件代替数字电路正好弥补这些缺陷。

2 CPLD简介和器件选型

利用可编程逻辑器件CPLD(Complex Programable Logic Device)设计硬件系统非常方便。工程师通过传统的原理图输入法,或是硬件描述语言自由设计数字系统。通过软件仿真验证事先设计的正确性。在PCB完成后,还可利用CPLD在线修改能力,随时修改设计而不必改动硬件电路。因此,使用CPLD可大大加快硬件电路设计进程,减少PCB面积,提高系统可靠性。

根据所需逻辑门数量以及将与其连接的电路引脚数,选用ALTERA公司的EPM570T144C5型CPLD,该器件采用TQFP144封装,内部有570个逻辑单元,相当于440个宏单元,而此前常用的EPM7128只有128个宏单元。

EPM570T144C5内部有2个I/O分区,共116个通用I/O,引脚延时为8.8 ns,满足位置检测系统所需的90多个通用I/O和延时不超过10 ns的设计要求。

3 位置检测系统组成

在介绍位置检测系统前,先简要介绍伺服电机控制系统(图1)。CPLD先对伺服电机光电编码器上发出的反馈信号进行译码、四倍频鉴相计数,然后将计数值存入锁存器,当用于电机控制的DSP控制器对CPLD进行读操作时,CPLD将锁存器里的计数值通过三态门输出给DSP控制器,由其控制电机的位移和速度。

位置检测系统采用CPLD器件实现硬件电路功能,用VHDL语言编程实现译码器、四倍频鉴相计数器、选通器等模块。图2为位置检测系统组成原理图。图2 中,光电编码器A和四倍频鉴相计数器A(光电编码器B和四倍频鉴相计数器B)构成单轴计数电路,将两个单轴计数电路配合译码器、选通器则构成双轴计数电路,就是用译码器控制选通器,以选通两个计数器的计数结果并传输到总线.总线和选通器之间增加三态门进行控制。这样就实现双轴位置检测。

4 系统设计

该系统设计的主要部分为伺服电机控制系统中的位置检测系统。在Ouartus II开发环境下设计系统,系统设计包括四倍频鉴相计数器、二四译码器和选通器的VHDL程序设计,如图3所示。通过图2所示的原理框图,将该系统设计的各个模块组合起来形成顶层文件,构成双轴的检测系统。图3中YMO模块为译码电路,用来选通哪轴输出,Y0、Y2用来控制计数器的清零与计数,Y1控制选通器选通,译码器真值表如表1所示。

四倍频鉴相计数器的VHDL程序代码如下:

5 系统仿真

图4为系统仿真结果。当译码器控制信号AB=00时,可看出 A1超前B1,所以轴1正转;B2超前A2所以轴2反转。

三态门使能信号EN=1时,数据选择器选通G口所对应的汁数器,即轴2,清零F口对应计数器,即对轴1清零。并将计数结果传输到总线,输出信号H从FFF 变化到FF8表明轴2反转,因此汁数器逆向计数。同时在AB译码器控制信号改变时和轴1,轴2正反转的其他情况时,仿真结果均正确,满足双轴位置检测系统设计。

6 结束语

在现代数控系统中,采用 CPLD实现位置检测系统已成为主流。新一代CPLD产品MAX II EPM570以面积小、集成度高和 GPIO口多等特点使得电路板集成度和抗干扰性都得以提高,方便结合DSP控制伺服电机位臀。总之,CPLD器件的发展使得逻辑电子电路的设计更灵活、方便。它将推动数控机床甚至工业各领域的发展。

传感器 变压器 编码器 电路 CPLD 仿真 PCB LTE DSP VHDL 总线 电子 相关文章:

- 基于FPGA的高速图像采集系统设计(03-30)

- 在单个FPGA平台上采用多种工业以太网标准进行设计(03-13)

- 基于CPLD的CCD信号发生器的研究(04-08)

- 在嵌入式设计中降低CPLD的功耗(04-30)

- Xilinx FPGA的功耗优化设计(04-08)

- 基于太空级Virtex FPGA的灵活高性能计算平台(04-08)