基于FPGA的微型数字存储系统设计方案

时间:11-08

来源:互联网

点击:

4 系统可靠性验证

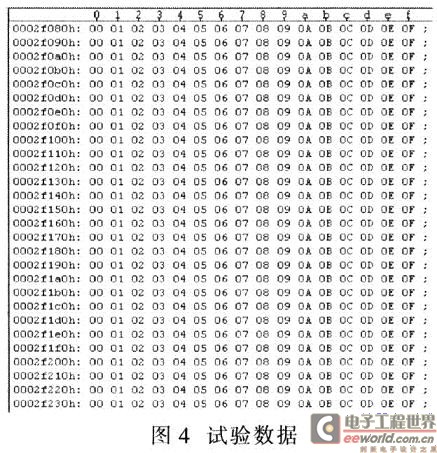

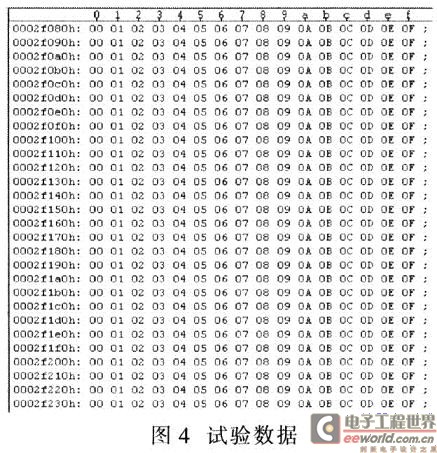

为验证系统可靠性,在数据输入端循环输入00"0F递增数据,通过上位机读出、写入Flash中的数据,图4为试验数据。通过读出的数据验证了该系统数据存储及回读的正确性、可靠性。

5 结束语

采用FPGA对Flash进行读、写、擦除操作,利用状态机分时控制3种操作,简化程序设计,简单修改地址将Flash的容量从32 MB增加到1 GB,提高了系统的可移植性、可扩展性和通用性,便于维护设备,有利于产品的优化和改进,缩短了开发周期。采用USB单片机与PC机建立通信连接,与现有设备很好兼容,数据读取速度可达1O MB/s,可方便、快捷地读取数据。通过多次验证,该系统工作稳定、可靠。

为验证系统可靠性,在数据输入端循环输入00"0F递增数据,通过上位机读出、写入Flash中的数据,图4为试验数据。通过读出的数据验证了该系统数据存储及回读的正确性、可靠性。

5 结束语

采用FPGA对Flash进行读、写、擦除操作,利用状态机分时控制3种操作,简化程序设计,简单修改地址将Flash的容量从32 MB增加到1 GB,提高了系统的可移植性、可扩展性和通用性,便于维护设备,有利于产品的优化和改进,缩短了开发周期。采用USB单片机与PC机建立通信连接,与现有设备很好兼容,数据读取速度可达1O MB/s,可方便、快捷地读取数据。通过多次验证,该系统工作稳定、可靠。

FPGA 电路 连接器 集成电路 单片机 电压 USB DSP Cypress 总线 VHDL Keil 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)