便携式产品具有低功耗意识的FPGA设计方法

时间:11-08

来源:互联网

点击:

通过降低逻辑的翻转率来降低动态功耗

首先在设计中,需要尽量避免不必要的翻转,可以通过下面几个步骤来实现这一目标:首先分析哪些逻辑的翻转是不必要的,随后对不必要的逻辑翻转的传播进行限制,展开逻辑翻转的时间。

减少逻辑可能产生的毛刺,先标识出翻转率高的网络以及它们的驱动,然后对驱动单元输入的最坏时序情况做评估,随后将毛刺的源往前调或往后调,然后对驱动单元的输入的最坏时序情况做评估,最后在驱动的逻辑后面插入一级触发器,根据先前的评估情况来决定用路径上其他时序元件的相同时钟沿或者相反的时钟沿来驱动触发器。即使是在单周期路径上面,如果有足够的slack来增加一个与门以及相关走线,那么就可以用与门的另外一个输入(毛刺源驱动寄存器)的反相时钟沿,从而减少毛刺。在某些情况下,可以通过伸展反转时间来降低毛刺的峰值功耗。

建议设计者要了解最终系统的运行模式,以及每种模式下系统的功耗概况。如果系统处于睡眠模式或者关闭模式的时间较长,需要观察浪涌电流和编程电流的影响,并处理好静态功耗。需要检查设计的动态功耗概况,找出功耗的主要瓶颈,根据概括表(图5"图8)找出最好的解决方法。

图5 RAM 动态功耗概括表

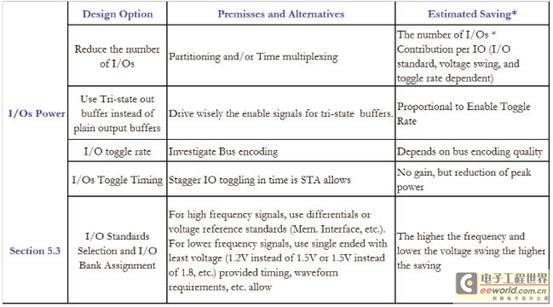

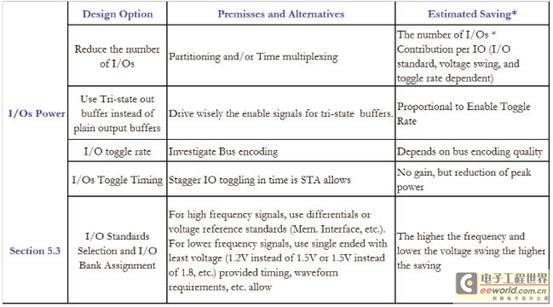

图6 I/O功耗概括表

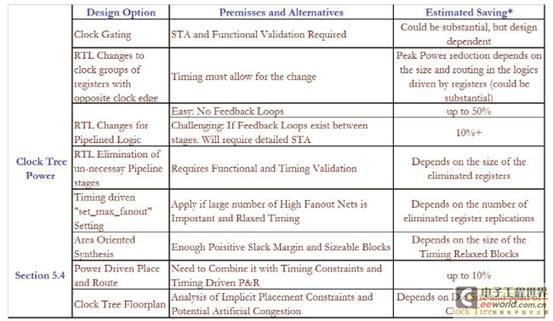

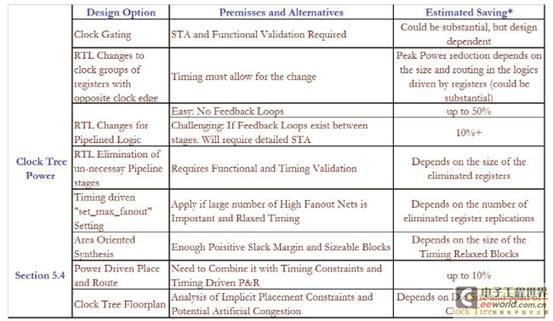

图7 时钟树功耗概括表

图8 逻辑功耗概括表

在对照概括表之前,只要时序允许,可以修改RTL代码;保证修改以后的功能和时序有效性;也可以尝试调整综合选项以及使用基于功耗优先的策略来进行布局布线。

首先在设计中,需要尽量避免不必要的翻转,可以通过下面几个步骤来实现这一目标:首先分析哪些逻辑的翻转是不必要的,随后对不必要的逻辑翻转的传播进行限制,展开逻辑翻转的时间。

减少逻辑可能产生的毛刺,先标识出翻转率高的网络以及它们的驱动,然后对驱动单元输入的最坏时序情况做评估,随后将毛刺的源往前调或往后调,然后对驱动单元的输入的最坏时序情况做评估,最后在驱动的逻辑后面插入一级触发器,根据先前的评估情况来决定用路径上其他时序元件的相同时钟沿或者相反的时钟沿来驱动触发器。即使是在单周期路径上面,如果有足够的slack来增加一个与门以及相关走线,那么就可以用与门的另外一个输入(毛刺源驱动寄存器)的反相时钟沿,从而减少毛刺。在某些情况下,可以通过伸展反转时间来降低毛刺的峰值功耗。

建议设计者要了解最终系统的运行模式,以及每种模式下系统的功耗概况。如果系统处于睡眠模式或者关闭模式的时间较长,需要观察浪涌电流和编程电流的影响,并处理好静态功耗。需要检查设计的动态功耗概况,找出功耗的主要瓶颈,根据概括表(图5"图8)找出最好的解决方法。

图5 RAM 动态功耗概括表

图6 I/O功耗概括表

图7 时钟树功耗概括表

图8 逻辑功耗概括表

在对照概括表之前,只要时序允许,可以修改RTL代码;保证修改以后的功能和时序有效性;也可以尝试调整综合选项以及使用基于功耗优先的策略来进行布局布线。

FPGA CPLD 电压 电流 汽车电子 PCB 电容 总线 电阻 电路 放大器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)