FPGA与ADSP TS201的总线接口设计方案

时间:11-08

来源:互联网

点击:

- 2.3 32位数据总线,64位寄存器

前面提到,突发流水协议与普通流水协议数据传输机制是一样的,只是多了一个指示信号BRST,当写操作时,FPGA如果在前一时钟沿采到地址、WRx、BRST信号有效,在下一时钟沿就锁存数据到寄存器低位,而如果在前一时钟沿采到地址、WRL有效,而BRST信号无效,在下一时钟沿就锁存数据到寄存器高位。同样,当读操作时,FPGA如果采到地址、RD、BRST信号有效,就将寄存器低位驱动到数据总线上,而如果采到地址、RD有效,BRST而信号无效,就将寄存器高位驱动到数据总线上,具体在哪个时钟沿驱动,由流水深度决定。

3 DSP设置

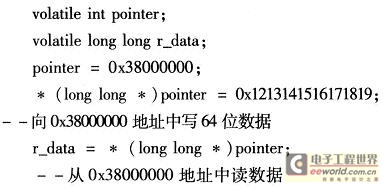

ADSP TS201与FPGA通信时,DSP是否采用流水协议,数据总线位宽,以及流水深度都可以通过系统配置寄存器SYSCON进行设置,SYSCON详细设置见文献,以32位数据总线访问64位寄存器为例,一级流水,SYSCON设置为

4 结束语

文中实现了DSP通过外部总线接口访问FPGA内部寄存器,但是如果需要传输的数据量很大,或者DSP与FPGA的时钟不同步,就不能用寄存器来实现,需要借助于双口RAM或者FIFO,读者可以在本文的基础上加以改进。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)