利用FPGA来实现RC6算法的设计与研究

时间:11-08

来源:互联网

点击:

RC6是作为AES(Advanced Encryption Standard)的候选算法提交给NIST(美国国家标准局)的一种新的分组密码。它是在RC5的基础上设计的,以更好地符合AES的要求,且提高了安全性,增强了性能。根据AES的要求,一个分组密码必须处理128位输入/输出数据。尽管RC5是一个非常快的分组密码,但它处理128位分组块时用了2个64位工作寄存器;而AES目前在讲究效率和简洁方面不支持64位操作,于是RC6修正这个错误,使用4个32位寄存器而不是2个64位寄存器,以更好地实现加解密。利用FPGA来实现RC6算法,可以提高运算速度。芯片设计为RC6算法处理器,辅助计算机处理器完成加解密操作,可以方便地实现对加解密的分析和研究。因此,此芯片可以作为协处理器来看待。

1 RC6算法

1.1 RC6算法概述

RC6秉承了RC5设计简单、广泛使用数据相关的循环移位思想,同时增强了抵抗攻击的能力,改进了RC5中循环移位的位数不依赖于寄存器中所有位的不足。RC6新的特色是输入的明文由原先2个区块扩展为4个,另外在运算方面则是使用了整数乘法,而整数乘法的使用则在每一个运算回合中增加了扩散(diffusion)的行为,并且使得即使很少的回合数也有很高的安全性。同时,RC6中所用的操作可以在大部分处理器上高效率地实现,提高了加密速度。RC6是一种安全、架构完整而且简单的区块加密法。它提供了较好的测试结果和参数方面相当大的弹性。RC6可以抵抗所有已知的攻击,能够提供AES所要求的安全性,可以说是近几年来相当优秀的一种加密法。

RC6不再使用2个64位工作寄存器,而是用4个32位寄存器。这就使得在每次循环中要进行2次循环移位操作,让更多的数据位来决定循环次数。RC6把明文分别存在4个区块A、B、C、D,刚开始分别包含明文的初始值,加密运算后则为4个密文的输出值。

1.2 RC6的工作原理

RC6是参数变量的分组算法,实际上是由3个参数确定的一个加密算法族。一个特定的RC6可以表示为RC6一w/r/b,3个参数w、r和b分别为字长、循环次数和密钥长度。AES中,w=32,r=20。本设计中,密钥长度b为128位(16字节)。RC6用4个w位的寄存器A、B、C、D来存放输入的明文和输出的密文。明文和密文的第一个字节存放在A的最低字节,经过加解密后,得到的明文和密文的最后一个字节存放在D的最高字节。

1.2.1 RC6一w/r/b基本运算

基本运算共有如下6种:①模2w加算运算,表示为“+”;②模2w减法运算,表示为“一”;③逐位异或运算,表示为“⊕”;④循环左移,字a循环左移b位表示为“a<<<b”;⑤循环右移,字a循环右移b位表示为“a>>>b”;⑥模2w乘法,表示为“×”。

1.2.2 RC6一w/r/b加密算法

输入:明文存放在4个w位输入寄存器A、B、C、D

式中:e一2.782 818 284 59…(自然对数);φ=1.618 033 988 749…(黄金分割)

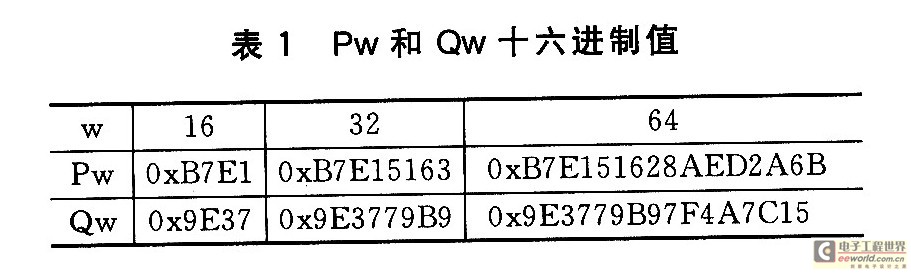

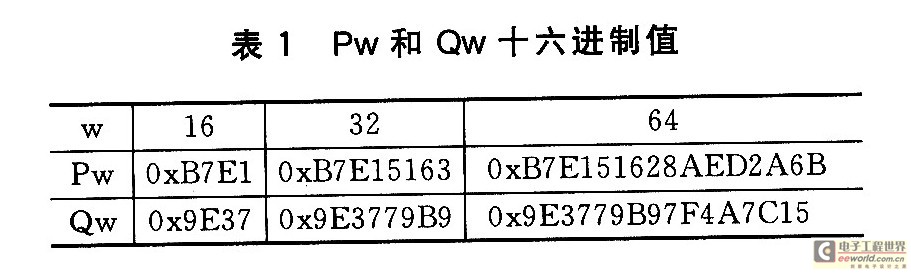

当w分别为16、32、64时,常数Pw、Qw分别如表1所列。在本设计中,w=16,输入为128位的主密钥,得到的是44个32位子密钥。

2 RC6加解密算法协处理器设计

2.1 RC6协处理器的顶层结构设计

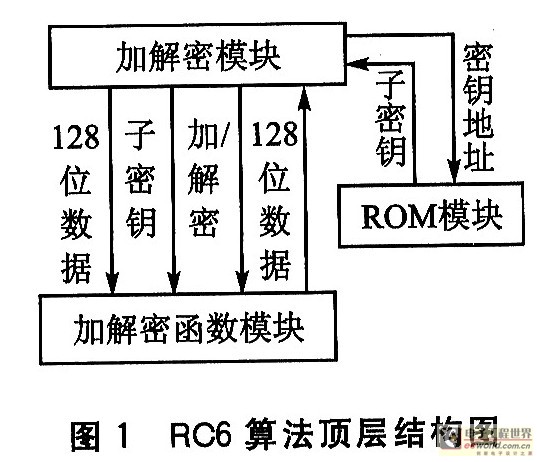

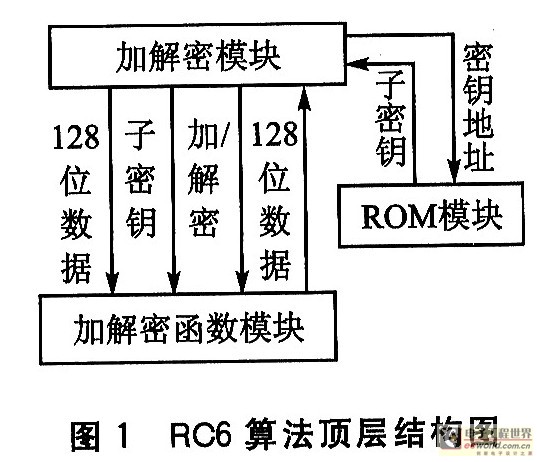

RC6协处理器包含以下3个模块:加解密模块,加解密函数模块和ROM模块。顶层结构如图1所示。

加解密模块:包括输入和输出、加/解密选择、状态机,以及函数调用声明和ROM调用取址。用于输入128位明文或密文,并且利用一个状态机定义程序顺序执行和保证循环控制,实现对ROM的44个子密钥读取,以及将数据输入函数中进行处理。由于输入ROM的地址是在一个时钟控制下,子密钥数据的输出有一定的延时,所以利用一个控制变量cnt实现地址提前一个时钟左右输入ROM,ROM接收到后输出子密钥,使在进行数据加解密处理时,已经有准备好的子密钥调用。

加解密函数模块:利用work用户自定义函数库,定义算法中用到的函数。其中包括5个函数,分别是:RFunct、afunct、cfunct、lshift、rshift。顶层文件循环调用此函数21次,进行加解密运算。

ROM模块:先在QuartusII里面将预定义的子密钥输入rc6keyrom.mif文件中,调用QuartusII的MegaWizardPlug—In Manager,自动生成ROM,供顶层文件调用。需要提前利用QuartusII建立一个.mif文件,将子密钥的数据输入。

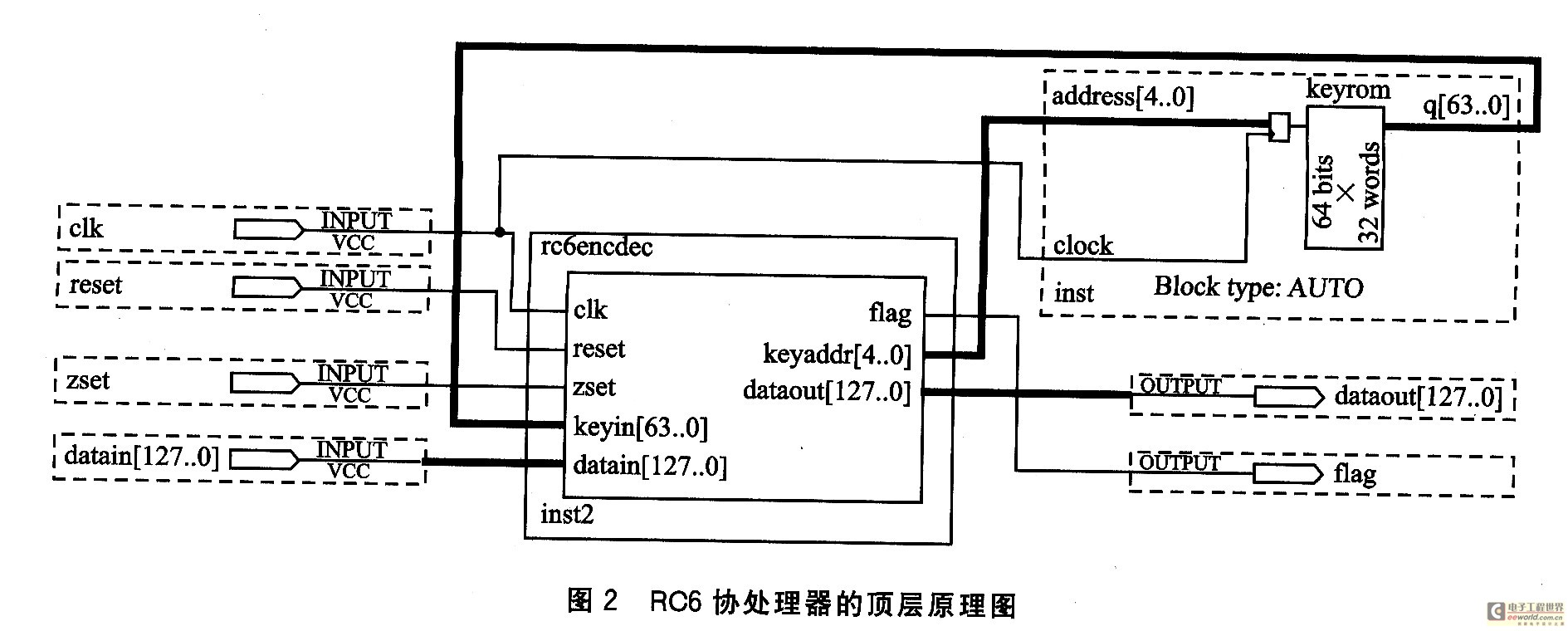

2.2 RC6协处理器的顶层原理图

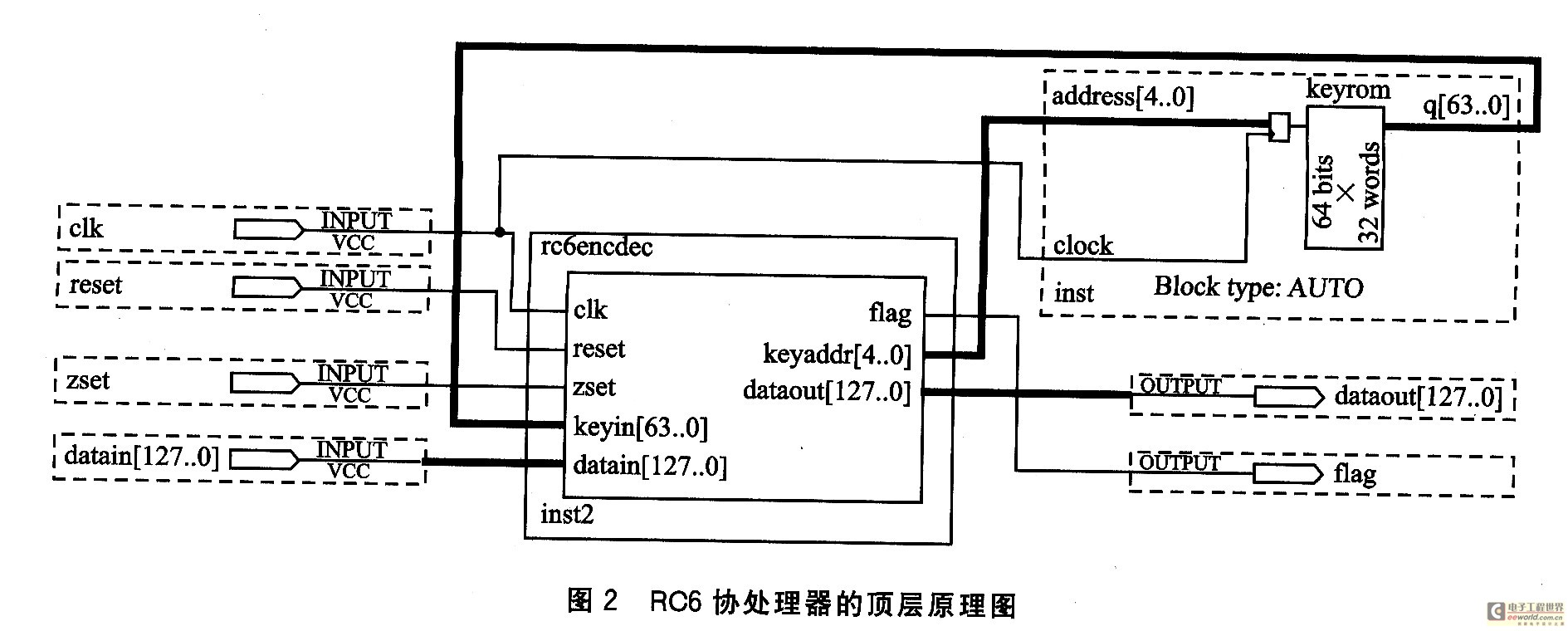

如图2所示,基于FPGA的RC6算法协处理器分3个模块:顶层模块、RC6加解密函数模块和ROM模块。共有260个I/0口,包括131输入端口和129个输出端口。

1 RC6算法

1.1 RC6算法概述

RC6秉承了RC5设计简单、广泛使用数据相关的循环移位思想,同时增强了抵抗攻击的能力,改进了RC5中循环移位的位数不依赖于寄存器中所有位的不足。RC6新的特色是输入的明文由原先2个区块扩展为4个,另外在运算方面则是使用了整数乘法,而整数乘法的使用则在每一个运算回合中增加了扩散(diffusion)的行为,并且使得即使很少的回合数也有很高的安全性。同时,RC6中所用的操作可以在大部分处理器上高效率地实现,提高了加密速度。RC6是一种安全、架构完整而且简单的区块加密法。它提供了较好的测试结果和参数方面相当大的弹性。RC6可以抵抗所有已知的攻击,能够提供AES所要求的安全性,可以说是近几年来相当优秀的一种加密法。

RC6不再使用2个64位工作寄存器,而是用4个32位寄存器。这就使得在每次循环中要进行2次循环移位操作,让更多的数据位来决定循环次数。RC6把明文分别存在4个区块A、B、C、D,刚开始分别包含明文的初始值,加密运算后则为4个密文的输出值。

1.2 RC6的工作原理

RC6是参数变量的分组算法,实际上是由3个参数确定的一个加密算法族。一个特定的RC6可以表示为RC6一w/r/b,3个参数w、r和b分别为字长、循环次数和密钥长度。AES中,w=32,r=20。本设计中,密钥长度b为128位(16字节)。RC6用4个w位的寄存器A、B、C、D来存放输入的明文和输出的密文。明文和密文的第一个字节存放在A的最低字节,经过加解密后,得到的明文和密文的最后一个字节存放在D的最高字节。

1.2.1 RC6一w/r/b基本运算

基本运算共有如下6种:①模2w加算运算,表示为“+”;②模2w减法运算,表示为“一”;③逐位异或运算,表示为“⊕”;④循环左移,字a循环左移b位表示为“a<<<b”;⑤循环右移,字a循环右移b位表示为“a>>>b”;⑥模2w乘法,表示为“×”。

1.2.2 RC6一w/r/b加密算法

输入:明文存放在4个w位输入寄存器A、B、C、D

式中:e一2.782 818 284 59…(自然对数);φ=1.618 033 988 749…(黄金分割)

当w分别为16、32、64时,常数Pw、Qw分别如表1所列。在本设计中,w=16,输入为128位的主密钥,得到的是44个32位子密钥。

2 RC6加解密算法协处理器设计

2.1 RC6协处理器的顶层结构设计

RC6协处理器包含以下3个模块:加解密模块,加解密函数模块和ROM模块。顶层结构如图1所示。

加解密模块:包括输入和输出、加/解密选择、状态机,以及函数调用声明和ROM调用取址。用于输入128位明文或密文,并且利用一个状态机定义程序顺序执行和保证循环控制,实现对ROM的44个子密钥读取,以及将数据输入函数中进行处理。由于输入ROM的地址是在一个时钟控制下,子密钥数据的输出有一定的延时,所以利用一个控制变量cnt实现地址提前一个时钟左右输入ROM,ROM接收到后输出子密钥,使在进行数据加解密处理时,已经有准备好的子密钥调用。

加解密函数模块:利用work用户自定义函数库,定义算法中用到的函数。其中包括5个函数,分别是:RFunct、afunct、cfunct、lshift、rshift。顶层文件循环调用此函数21次,进行加解密运算。

ROM模块:先在QuartusII里面将预定义的子密钥输入rc6keyrom.mif文件中,调用QuartusII的MegaWizardPlug—In Manager,自动生成ROM,供顶层文件调用。需要提前利用QuartusII建立一个.mif文件,将子密钥的数据输入。

2.2 RC6协处理器的顶层原理图

如图2所示,基于FPGA的RC6算法协处理器分3个模块:顶层模块、RC6加解密函数模块和ROM模块。共有260个I/0口,包括131输入端口和129个输出端口。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)