对基于FPGA的高斯白噪声发生器的研究与设计

时间:11-08

来源:互联网

点击:

3 实验结果

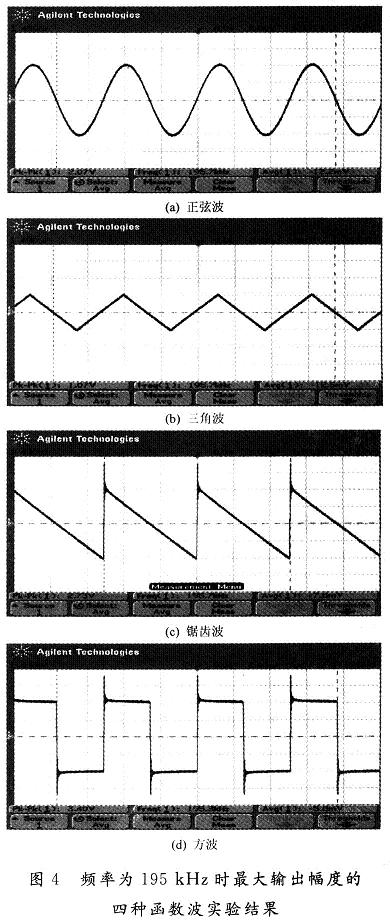

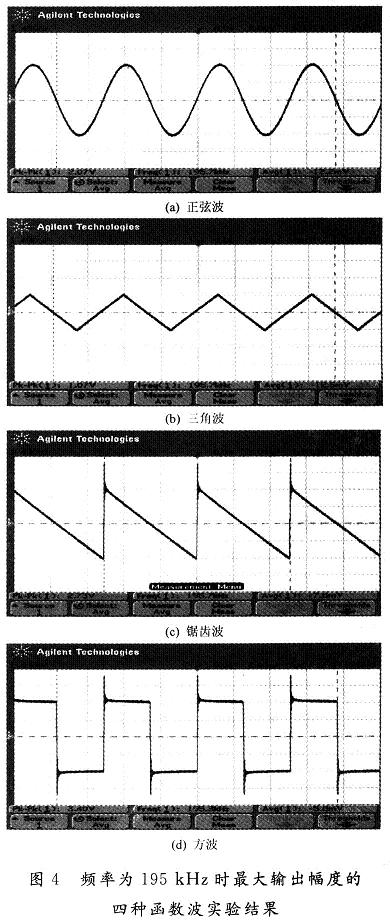

本文的FPGA平台选用Altera公司的EP2C8现场可编程逻辑器件,完成所有m序列、FIR数字滤波和DDS算法,需要FPGA 86%的逻辑单元资源和1%的RAM资源;时钟采用50MHz、稳定度为50 ppm的有源晶振,通过EP2C8内部PLL(Phase Locked Loop,锁相环)3倍频到150 MHz作为系统全局时钟;采用ADI公司的AD9731进行D/A转换,采样速度150 MSPS,10位;对AD9731输出的电流信号进行7阶LC低通滤波,然后进行放大,使得噪声信号的满幅输出都达到峰峰值3V。图4是频率为195 kHz最大输出幅度的四种函数波测试结果。

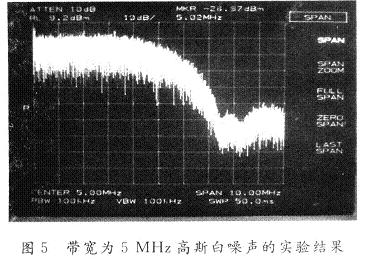

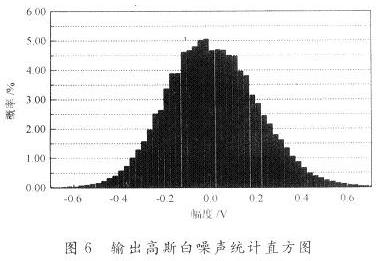

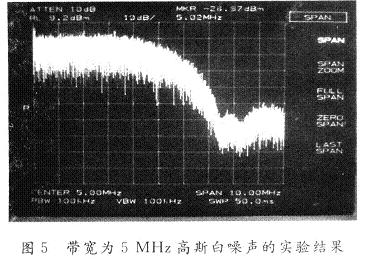

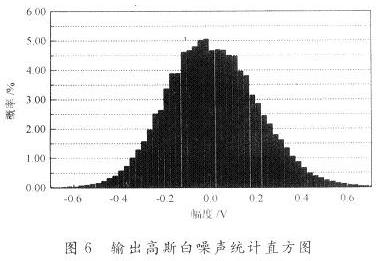

从图4可以看出,采用DDS模块,得到了正弦波、三角波、锯齿波和方波的波形。图5为该噪声和函数波发生器产生的5 MHz噪声的实验结果,图6是输出带宽为5 MHz的高斯白噪声统计直方图。

从图5和图6可以看出,基于FPGA的m序列发生算法,FIR滤波算法和DDS算法,通过数/模转换和低通放大后,本文设计的噪声发生器产生的5 MHz噪声的3 dB,带宽为4.8 MHz,带内平坦度为±1.5 dB,输出噪声的统计特性服从高斯分布,满足了设计需要。

4 结 语

设计了一种基于FPGA高斯白噪声发生器,分析了该种噪声发生器所用的m序列发生算法,FIR数字滤波算法和DDS算法,可产生带宽为3~66 MHz,步进3 MHz,幅度8位可调的高斯白噪声;采用现场可编程门阵列(FPGA)实现噪声发生器的设计,在Altera公司的QuartusⅡ软件环境下,实现了基于FPGA的m序列产生模块、FIR数字滤波器模块、DDS模块和合成模块,通过数/模转换器和低通放大,得到了可用于雷达系统和通信信道测试的高斯白噪声信号。实验结果验证了本文设计的有效性。

本文的FPGA平台选用Altera公司的EP2C8现场可编程逻辑器件,完成所有m序列、FIR数字滤波和DDS算法,需要FPGA 86%的逻辑单元资源和1%的RAM资源;时钟采用50MHz、稳定度为50 ppm的有源晶振,通过EP2C8内部PLL(Phase Locked Loop,锁相环)3倍频到150 MHz作为系统全局时钟;采用ADI公司的AD9731进行D/A转换,采样速度150 MSPS,10位;对AD9731输出的电流信号进行7阶LC低通滤波,然后进行放大,使得噪声信号的满幅输出都达到峰峰值3V。图4是频率为195 kHz最大输出幅度的四种函数波测试结果。

从图4可以看出,采用DDS模块,得到了正弦波、三角波、锯齿波和方波的波形。图5为该噪声和函数波发生器产生的5 MHz噪声的实验结果,图6是输出带宽为5 MHz的高斯白噪声统计直方图。

从图5和图6可以看出,基于FPGA的m序列发生算法,FIR滤波算法和DDS算法,通过数/模转换和低通放大后,本文设计的噪声发生器产生的5 MHz噪声的3 dB,带宽为4.8 MHz,带内平坦度为±1.5 dB,输出噪声的统计特性服从高斯分布,满足了设计需要。

4 结 语

设计了一种基于FPGA高斯白噪声发生器,分析了该种噪声发生器所用的m序列发生算法,FIR数字滤波算法和DDS算法,可产生带宽为3~66 MHz,步进3 MHz,幅度8位可调的高斯白噪声;采用现场可编程门阵列(FPGA)实现噪声发生器的设计,在Altera公司的QuartusⅡ软件环境下,实现了基于FPGA的m序列产生模块、FIR数字滤波器模块、DDS模块和合成模块,通过数/模转换器和低通放大,得到了可用于雷达系统和通信信道测试的高斯白噪声信号。实验结果验证了本文设计的有效性。

电子 电路 FPGA DAC 滤波器 放大器 仿真 低通滤波器 集成电路 电压 振荡器 Altera ADI 电流 Quartus 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)