基于MicroBlaze软核的液晶驱动程序设计

时间:11-08

来源:互联网

点击:

1 MicroBlaze的体系结构

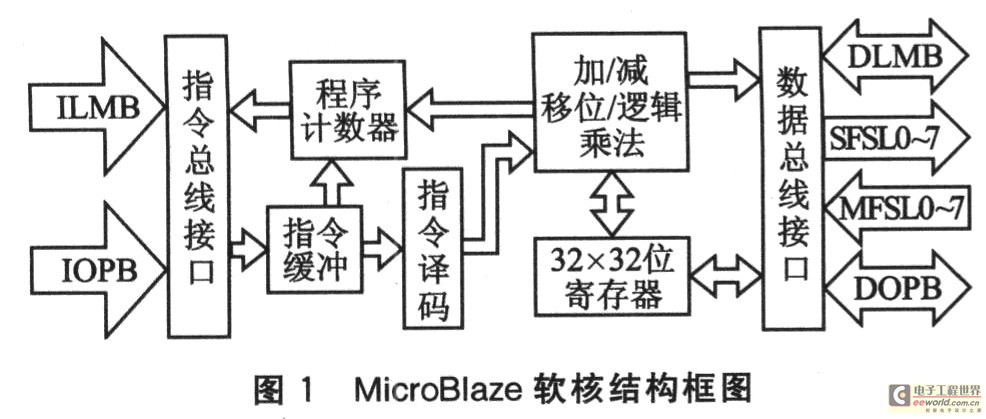

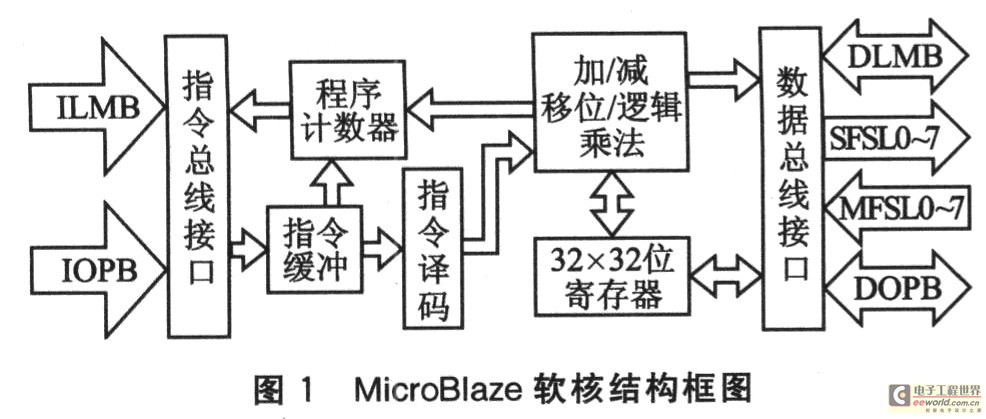

MicroBlaze采用功能强大的32位流水线结构,包含32个32位通用寄存器和1个可选的32位移位器,时钟频率可达150 MHz;在Virrex一4 FPGA上运行速率高达120 DMIPS,仅占用Virtex—II Pro FPGA中的950个逻辑单元。MicroBlaze软核的结构框图如图1所示。它具有以下基本特征:

①32个32位通用寄存器和2个专用寄存器(程序计数器和状态标志寄存器)。

②32位指令系统,支持3个操作数和2种寻址方式。

③分离的32位指令和数据总线,符合IBM的OPB总线规范(与外设相连接的低速总线)。

④通过本地存储器总线(LMB,本地高速总线)直接访问片内块存储器(BRAM)。

⑤具有高速的指令和数据缓存(cache),三级流水线结构(取址、译码、执行)。

⑥具有硬件调试模块(MDM)。

⑦带8个输入和8个输出快速链路接口(FSL)。

图中接口信号说明如下:

①DOPB,器件内部的外围设备数据接口总线,用于处理器与片内的设备进行数据交换。

②DLMB,实现数据交换的本地块存储器总线。该总线为处理器内核与块存储器(BRAM)之间提供专用的高速数据交换通道。

③IOPB,用于实现外部程序存储器的总线接口。当程序较大时,需要外接大容量的存储器。该总线提供读取指令的通道。

④ILMB,用于取指令的本地存储器总线。该总线与器件内部的块存储器(BRAM)相连,实现高速的指令读取。

⑤MFSLO~7,主设备数据接口,提供点对点的通信通道。

⑥SFSLO~7,从设备数据接口,提供点对点的通信通道。

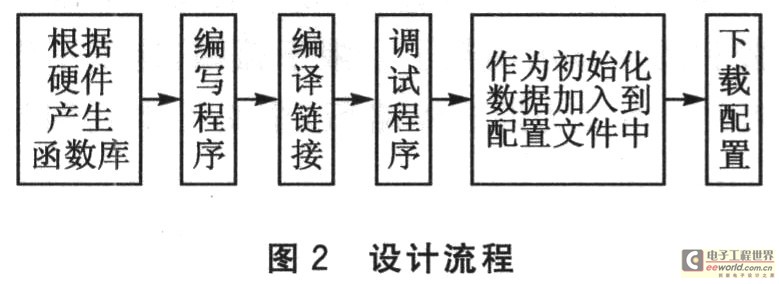

2 MicroBlaze嵌入式开发工具EDK

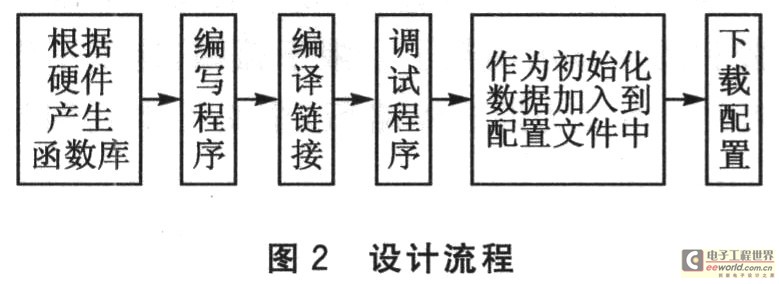

Xilinx公司提供了完善的嵌入式开发工具EDK(Em—bedded Development Kit)。EDK是Xilinx公司于2003年推出的SOPC(System On Programmable Chip)系统开发套件。该套件集成了丰富的开发工具和大量的IP核资源,其中集成的工具包括硬件平台生成器(PlatGen)、硬件仿真模型生成器(SimGen)、硬件调试工具(XMD)、软件库生成器(LibGen)、应用软件编译工具(GNU Compilers)、软件调试工具(GNU Debuggers)等;IP核资源包括LMB和OPB总线接口、外部存储器控制器(EMC)、SDRAM控制器、UART接口、中断控制器、定时器等。所有这些工具和资源都由EDK中的一个叫平台工作室XPS(XilinxPlatform Studio)的集成开发环境统一管理。XPS提供一个友好的图形用户界面(GUI),使用非常方便。设计流程如图2所示。

3 液晶显示模块

MPG240128液晶模块为图形点阵式液晶,不仅可以显示数字、字符等内容,还可以显示汉字和任意图形。该模块的控制芯片为T6963C,与外部的连接只有8位数据线和6条控制线及电源。液晶模块引脚说明如表1所列。MCtJ只要通过这些数据线和控制线,按照相应的时序进行读写,即可实现对模块的显示控制。

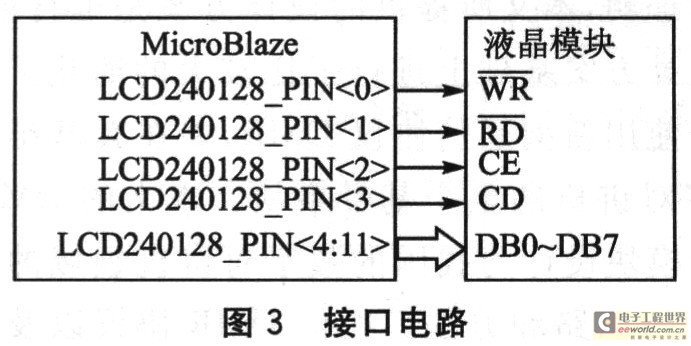

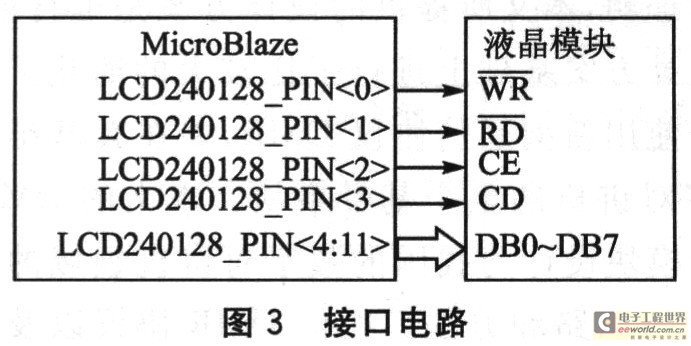

4 MicrOBlaze与液晶显示模块的接口

由于本文采用的液晶模块已经自带了显示控制芯片T6963C,因此液晶模块的外围电路相对来说就比较简单,只要考虑和MicroBlaze的接口电路即可。本设计采用GPIO模拟液晶模块的时序,实现对液晶模块的显示控制。MicroBlaze和液晶模块的接口电路如图3所示。

在EDK开发套件的XPS集成开发环境下进行系统硬件设计。在其界面环境下,添加所需IP核,进行系统连接和各项参数设置。利用平台产生器,根据硬件描述文件(.MHS文件),生成嵌入式系统子模块的网表文件(.NGC),然后调用Xilinx的综合工具XST进行综合,从而构成整个应用系统的硬件模型。

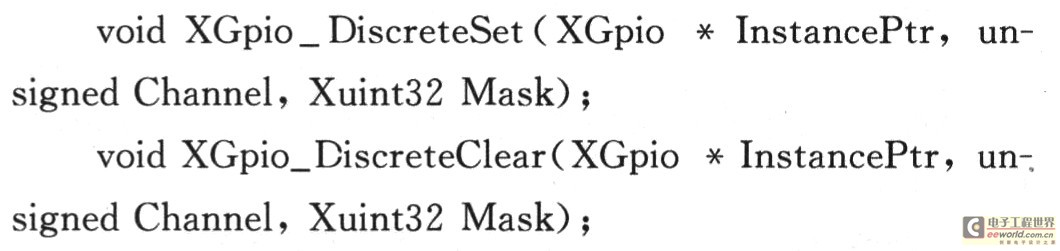

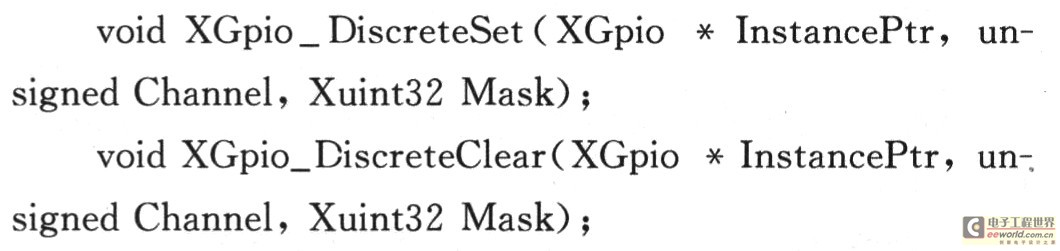

本设计中采用了GPIO对液晶模块进行控制。EDK提供了一系列API函数,通过这些函数可以很方便地对GPIO进行操作。下面先介绍2个函数:

其中,InstancePtr是指针,指向要控制的GPIO的基地址;Channel为通道值,选0或1。这两个函数只对Mask中对应位为1的位有影响,比如,XGpio_DiscreteSet(&lcd240128,1,Ox00000001)将LCl3240128_pin<O>置1,而不影响其他位;同理,XGpio_DiscteteClear(&1cd240128,1,0x00000001)将LCD240128_pin<0>置0,而不影响其他位。为了增强程序的可读性,增加了8个宏定义:#define wr_high()XGpio_DiscreteSet(&lcd240128,1,Ox00000800),#define wr_low()XGpio_DiscreteClear(&1cd240128,l,0x00000800),其他6个同理可推知。有了这2个函数,就可以很方便地编写出写命令和写数据函数了。下面对这2个函数作简要介绍:

液晶显示图形和字符都是由点阵组成的,因此,在液晶上显示一个像素点是显示图形和字符的基础。下面将单像素点显示函数介绍如下:

有了单像素点显示函数,就可以很方便地编写出字符显示函数和图形显示函数了。限于篇幅,这里不作介绍。

MicroBlaze采用功能强大的32位流水线结构,包含32个32位通用寄存器和1个可选的32位移位器,时钟频率可达150 MHz;在Virrex一4 FPGA上运行速率高达120 DMIPS,仅占用Virtex—II Pro FPGA中的950个逻辑单元。MicroBlaze软核的结构框图如图1所示。它具有以下基本特征:

①32个32位通用寄存器和2个专用寄存器(程序计数器和状态标志寄存器)。

②32位指令系统,支持3个操作数和2种寻址方式。

③分离的32位指令和数据总线,符合IBM的OPB总线规范(与外设相连接的低速总线)。

④通过本地存储器总线(LMB,本地高速总线)直接访问片内块存储器(BRAM)。

⑤具有高速的指令和数据缓存(cache),三级流水线结构(取址、译码、执行)。

⑥具有硬件调试模块(MDM)。

⑦带8个输入和8个输出快速链路接口(FSL)。

图中接口信号说明如下:

①DOPB,器件内部的外围设备数据接口总线,用于处理器与片内的设备进行数据交换。

②DLMB,实现数据交换的本地块存储器总线。该总线为处理器内核与块存储器(BRAM)之间提供专用的高速数据交换通道。

③IOPB,用于实现外部程序存储器的总线接口。当程序较大时,需要外接大容量的存储器。该总线提供读取指令的通道。

④ILMB,用于取指令的本地存储器总线。该总线与器件内部的块存储器(BRAM)相连,实现高速的指令读取。

⑤MFSLO~7,主设备数据接口,提供点对点的通信通道。

⑥SFSLO~7,从设备数据接口,提供点对点的通信通道。

2 MicroBlaze嵌入式开发工具EDK

Xilinx公司提供了完善的嵌入式开发工具EDK(Em—bedded Development Kit)。EDK是Xilinx公司于2003年推出的SOPC(System On Programmable Chip)系统开发套件。该套件集成了丰富的开发工具和大量的IP核资源,其中集成的工具包括硬件平台生成器(PlatGen)、硬件仿真模型生成器(SimGen)、硬件调试工具(XMD)、软件库生成器(LibGen)、应用软件编译工具(GNU Compilers)、软件调试工具(GNU Debuggers)等;IP核资源包括LMB和OPB总线接口、外部存储器控制器(EMC)、SDRAM控制器、UART接口、中断控制器、定时器等。所有这些工具和资源都由EDK中的一个叫平台工作室XPS(XilinxPlatform Studio)的集成开发环境统一管理。XPS提供一个友好的图形用户界面(GUI),使用非常方便。设计流程如图2所示。

3 液晶显示模块

MPG240128液晶模块为图形点阵式液晶,不仅可以显示数字、字符等内容,还可以显示汉字和任意图形。该模块的控制芯片为T6963C,与外部的连接只有8位数据线和6条控制线及电源。液晶模块引脚说明如表1所列。MCtJ只要通过这些数据线和控制线,按照相应的时序进行读写,即可实现对模块的显示控制。

4 MicrOBlaze与液晶显示模块的接口

由于本文采用的液晶模块已经自带了显示控制芯片T6963C,因此液晶模块的外围电路相对来说就比较简单,只要考虑和MicroBlaze的接口电路即可。本设计采用GPIO模拟液晶模块的时序,实现对液晶模块的显示控制。MicroBlaze和液晶模块的接口电路如图3所示。

在EDK开发套件的XPS集成开发环境下进行系统硬件设计。在其界面环境下,添加所需IP核,进行系统连接和各项参数设置。利用平台产生器,根据硬件描述文件(.MHS文件),生成嵌入式系统子模块的网表文件(.NGC),然后调用Xilinx的综合工具XST进行综合,从而构成整个应用系统的硬件模型。

本设计中采用了GPIO对液晶模块进行控制。EDK提供了一系列API函数,通过这些函数可以很方便地对GPIO进行操作。下面先介绍2个函数:

其中,InstancePtr是指针,指向要控制的GPIO的基地址;Channel为通道值,选0或1。这两个函数只对Mask中对应位为1的位有影响,比如,XGpio_DiscreteSet(&lcd240128,1,Ox00000001)将LCl3240128_pin<O>置1,而不影响其他位;同理,XGpio_DiscteteClear(&1cd240128,1,0x00000001)将LCD240128_pin<0>置0,而不影响其他位。为了增强程序的可读性,增加了8个宏定义:#define wr_high()XGpio_DiscreteSet(&lcd240128,1,Ox00000800),#define wr_low()XGpio_DiscreteClear(&1cd240128,l,0x00000800),其他6个同理可推知。有了这2个函数,就可以很方便地编写出写命令和写数据函数了。下面对这2个函数作简要介绍:

液晶显示图形和字符都是由点阵组成的,因此,在液晶上显示一个像素点是显示图形和字符的基础。下面将单像素点显示函数介绍如下:

有了单像素点显示函数,就可以很方便地编写出字符显示函数和图形显示函数了。限于篇幅,这里不作介绍。

FPGA MIPS 总线 嵌入式 Xilinx 仿真 EMC 电路 LCD 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)