基于FPGA滑动相关法伪码捕获的研究与实现

时间:11-08

来源:互联网

点击:

对于码分多址的扩频通信方式而言,只有当接收端本地伪码与发端伪码处于相同相位状态时,有用的信息才能被解出。因此,扩频序列相位的捕获与跟踪是扩频通信系统的关键,而伪码序列相位的捕获尤为重要。滑动相关法是常用的方法之一。扩频通信系统要求实时性,以及较高的数据处理速度,这正是FPGA的优势。所以在扩频通信系统中,大量应用FPGA芯片作为前级处理芯片。

实现原理

原理分析

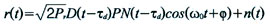

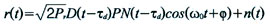

接收机端接收到的扩频信号可以表示为:

其中,P_{r}为接收信号功率,τ_{d}为传输时延,D(t)为信息码, PN(t)为伪码, n(t)为传输过程的加性噪声。扩频接收机要完成的任务就是去掉PN(T-τ_{d}) 伪码项和cos(ω_{0}t+φ) 载波项,从而得到信息数据DZ(t)。

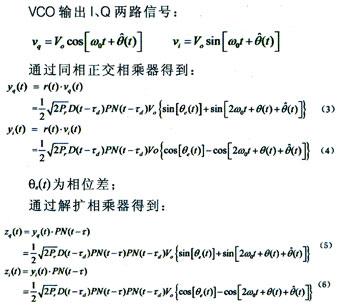

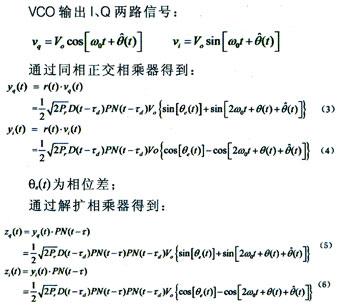

VCO输出I、Q两路信号:

通过同相正交相乘器得到:

利用PN码的相关特性,即相位对齐时,相关结果最大。当载波和码相位都对准时,经过累加清洗(低通滤波)输出为:

经过平方相加可去掉载波对相关结果的影响,得到相关峰。

实现框图

在直接序列扩频系统中,伪码的捕获是构成码同步系统的重要结构,也是直扩系统中必不可少的部分。接收机若要把伪码扩展的信号解出,接收方就必须能产生一个与发方一样的伪码序列(保证最大相关值),而且,该本地伪码速率、相位要与接收到的伪码保持一致。对于约定好的收、发方用同一个伪码很容易办到,但是,如果要从解扩相关器得到传送的信息,仅仅保证一样的码型是远远不够的。因为即使相同的伪随机码,当相位差大于一个码片时,它们的相关峰就完全消失。在实际通信中,由于收、发信机时钟的不稳定性,接收、发射时刻的不确定性,信道传输延迟及干扰等因素的影响,收、发伪码序列的相位差是随机的。因此解扩的第一步就是要在接收信号的伪码相位中捕获到一个与本地伪码一致的相位状态。当这种状态出现时相关器就会有一个相关峰值输出,峰值与门限相比,若超出则确定相位已捕捉到,立即停止捕捉动作,转入相位跟踪状态;若小于门限则改变本地码相位,继续进行捕获。系统实现原理如图1所示。

实现方法

根据相位捕获的方法可分为:连续相位滑动相关法和在此思路上改进的不连续相位相关法。

连续相位滑动相关法

此方法是通过改变本地伪码时钟速率,与发端伪码时钟速率保持一个合适偏移量,使接收信号中伪码相位与本地伪码相位在相关器内进行相对滑动。这种方法的相位捕获是连续进行的,所以相关峰值是一个连续量。相关值一旦超过捕获门限,标志正确相位已被搜索到,接收机立即恢复本地伪码时钟速率(收、发信机都使用稳定度很高的振荡源,所以它们的码速率可以基本保持一致),停止相位滑动,启动跟踪电路,使相位差进一步缩小(意味着相关性增大),获得更高解扩信噪比,满足其后解调门限要求。此种捕获方法捕获时间和检测概率相互矛盾。例如,对于一个N=215位的PN码,两伪码之间最大相对滑动速率约为5kc/ps,遍历其所有相关状态需要的时间为6.55S。在实际通信过程中,由于干扰及其它原因造成伪码相位失锁需要重新捕捉时,这么长的捕捉时间会严重影响通信质量,因而是不可取的。由以上分析可知,这种捕捉方法相位搜索精度高但同时导致了过长的捕捉时间,在实际中很少应用,但其思路值得借鉴。不连续滑动相关法就是在此基础上的改进。

不连续相位滑动相关法

所谓连续与不连续的区别是对搜索中相位的滑动变化量而言,后一种方法是把连续的相位搜索改为跳跃式的搜索,即两个码之间的相位滑动量不再是连续地以一定的步进量产生相位滑动。不连续滑动相关法是利用一个相位搜索电路,在捕获过程中使本地伪码相位以一定的步进值跳跃变化,这样遍历整个伪码时间大大减少。与前一种方法相比,它的收、发伪码时钟速率保持一致,从而不会造成码片宽度不一致,导致相关峰值下降。本地伪码与接收伪码相位的相对改变是靠搜索电路对伪码发生器时钟的超前、滞后控制来实现的,因此相位搜索电路(如图2所示)是不同于前者的关键所在。下面重点讨论实现半码片滑动的实现方法。

捕获方法1 (滑动步进为TC/2)

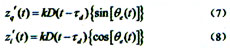

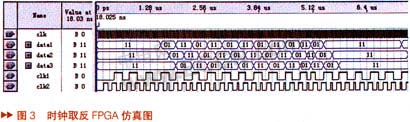

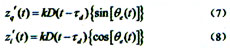

时钟取反法:

如图1所示,当信号包络的平方小于门限时,输出控制信号,对图2中CLK取反,取反的结果相当于利用原CLK时钟下降沿进行触发。经过二分频后作为伪码产生器的时钟,同时把CLK作为移位寄存器的时钟,三位移位寄存器的输出相当于移动了半个码片。FPGA仿真结果如图3所示。

图中data1,data2,data3,分别为三位移位寄存器的输出,01表示+1,11表示1,clk1为码NCO的输出,clk2为它的二分频。此方法在整个系统中要多次对时钟进行取反操作,会带来比较严重的时序问题,使系统工作时序满足不了。为了解决此问题,可采用改进的方法。

实现原理

原理分析

接收机端接收到的扩频信号可以表示为:

其中,P_{r}为接收信号功率,τ_{d}为传输时延,D(t)为信息码, PN(t)为伪码, n(t)为传输过程的加性噪声。扩频接收机要完成的任务就是去掉PN(T-τ_{d}) 伪码项和cos(ω_{0}t+φ) 载波项,从而得到信息数据DZ(t)。

VCO输出I、Q两路信号:

通过同相正交相乘器得到:

利用PN码的相关特性,即相位对齐时,相关结果最大。当载波和码相位都对准时,经过累加清洗(低通滤波)输出为:

经过平方相加可去掉载波对相关结果的影响,得到相关峰。

实现框图

在直接序列扩频系统中,伪码的捕获是构成码同步系统的重要结构,也是直扩系统中必不可少的部分。接收机若要把伪码扩展的信号解出,接收方就必须能产生一个与发方一样的伪码序列(保证最大相关值),而且,该本地伪码速率、相位要与接收到的伪码保持一致。对于约定好的收、发方用同一个伪码很容易办到,但是,如果要从解扩相关器得到传送的信息,仅仅保证一样的码型是远远不够的。因为即使相同的伪随机码,当相位差大于一个码片时,它们的相关峰就完全消失。在实际通信中,由于收、发信机时钟的不稳定性,接收、发射时刻的不确定性,信道传输延迟及干扰等因素的影响,收、发伪码序列的相位差是随机的。因此解扩的第一步就是要在接收信号的伪码相位中捕获到一个与本地伪码一致的相位状态。当这种状态出现时相关器就会有一个相关峰值输出,峰值与门限相比,若超出则确定相位已捕捉到,立即停止捕捉动作,转入相位跟踪状态;若小于门限则改变本地码相位,继续进行捕获。系统实现原理如图1所示。

实现方法

根据相位捕获的方法可分为:连续相位滑动相关法和在此思路上改进的不连续相位相关法。

连续相位滑动相关法

此方法是通过改变本地伪码时钟速率,与发端伪码时钟速率保持一个合适偏移量,使接收信号中伪码相位与本地伪码相位在相关器内进行相对滑动。这种方法的相位捕获是连续进行的,所以相关峰值是一个连续量。相关值一旦超过捕获门限,标志正确相位已被搜索到,接收机立即恢复本地伪码时钟速率(收、发信机都使用稳定度很高的振荡源,所以它们的码速率可以基本保持一致),停止相位滑动,启动跟踪电路,使相位差进一步缩小(意味着相关性增大),获得更高解扩信噪比,满足其后解调门限要求。此种捕获方法捕获时间和检测概率相互矛盾。例如,对于一个N=215位的PN码,两伪码之间最大相对滑动速率约为5kc/ps,遍历其所有相关状态需要的时间为6.55S。在实际通信过程中,由于干扰及其它原因造成伪码相位失锁需要重新捕捉时,这么长的捕捉时间会严重影响通信质量,因而是不可取的。由以上分析可知,这种捕捉方法相位搜索精度高但同时导致了过长的捕捉时间,在实际中很少应用,但其思路值得借鉴。不连续滑动相关法就是在此基础上的改进。

不连续相位滑动相关法

所谓连续与不连续的区别是对搜索中相位的滑动变化量而言,后一种方法是把连续的相位搜索改为跳跃式的搜索,即两个码之间的相位滑动量不再是连续地以一定的步进量产生相位滑动。不连续滑动相关法是利用一个相位搜索电路,在捕获过程中使本地伪码相位以一定的步进值跳跃变化,这样遍历整个伪码时间大大减少。与前一种方法相比,它的收、发伪码时钟速率保持一致,从而不会造成码片宽度不一致,导致相关峰值下降。本地伪码与接收伪码相位的相对改变是靠搜索电路对伪码发生器时钟的超前、滞后控制来实现的,因此相位搜索电路(如图2所示)是不同于前者的关键所在。下面重点讨论实现半码片滑动的实现方法。

捕获方法1 (滑动步进为TC/2)

时钟取反法:

如图1所示,当信号包络的平方小于门限时,输出控制信号,对图2中CLK取反,取反的结果相当于利用原CLK时钟下降沿进行触发。经过二分频后作为伪码产生器的时钟,同时把CLK作为移位寄存器的时钟,三位移位寄存器的输出相当于移动了半个码片。FPGA仿真结果如图3所示。

图中data1,data2,data3,分别为三位移位寄存器的输出,01表示+1,11表示1,clk1为码NCO的输出,clk2为它的二分频。此方法在整个系统中要多次对时钟进行取反操作,会带来比较严重的时序问题,使系统工作时序满足不了。为了解决此问题,可采用改进的方法。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)