在FPGA上对OC8051 IP核的修改与测试

时间:11-08

来源:互联网

点击:

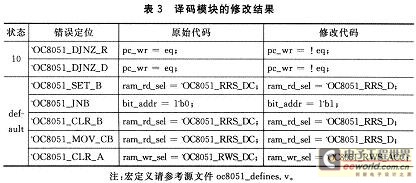

- (4)oc8051_decoder模块

该模块用于对指令译码。其设计思想是,分析当前输入信号op_in和所处状态state,把指令的功能配置为其他模块的控制信号,并得出下一个状态。因为各指令的指令周期不同,所以每条指令译码执行状态也各有不同。模块主体由状态机构成,在每个状态下对状态机不同的执行状态进行条件判断嵌套,以此实现对不同指令的多路选择。对模块仿真时发现,执行如DJNZ、JB、CLR等指令的结果不正确,其原因是在某些状态下对某些指令的译码有误,主要表现为配置了错误的控制信号。对模块修改结果如表3所列。

2.3 仿真结果

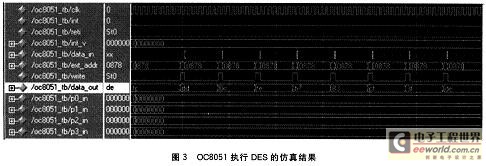

程序执行方式是单片机的基本工作方式,通常可以分为单步执行和连续执行两种。事实上,2.2小节中的具体修改方法正是结合这两种工作方式实现的。数据加密标准(DES)是著名的对称密钥分组密码,由美国标准FIPS 46-2定义。基于8051指令系统,DES的软件实现难度不大,但它是对OC8051 IP核工作能力的一次综合检验。采用DEs标准测试向量:

密钥K=1A624C89520DEC46

明文P=748502CD38451097

密文C=DD0CFEB783CF3FDE

结合图2所示的仿真调试方案,Modelsim环境中OC8051执行DES的仿真结果如图3所示。

3 基于FPGA的下载测试

利用FPGA对其功能进行了验证。选用Altera公司的EP2C35F672C6型号FPGA开发板,含有33 216个逻辑单元(LE)、丰富的存储器(RAM)和4个锁相环(PLL)。采用QuartusII软件,OC8051 IP核综合后占用3 917个逻辑单元,时钟频率最高达到30.81 MHz,FPGA测试的实际频率为27 MHz。

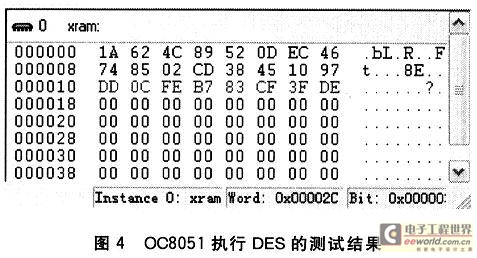

利用QuartusII对OC8051 IP核综合、布局布线后,采用JTAG方式将配置文件下载至FPGA中,测试程序仍采用DES算法程序。In-System Memory ContentEditor是QuartusII提供的一个可在线操作FPGA片上RAM内容的工具,通过JTAG方式,用户可以查看和修改RAM中的内容。如果用户设计对RAM中的内容进行了修改,需要查看修改后的结果是否为所期望的,则使用该工具最为方便。OC8051 IP核外部RAM中的数据可以通过该工具方便地操作,所以本文对DES测试向量的输入和输出都是通过它来完成的,如图4所示。

FPGA下载测试结果表明,OC8051工作正常,与仿真结果一样,测试程序运行正确。

结 语

本文介绍了一种OC8051 IP核的仿真测试方案。该方案给出了查找与定位IP核中逻辑错误的方法,并详细介绍了各种错误的修改方法。测试结果表明,OC8051工作正常,已经初步具备了微控制器的功能,可以被运用于实际的工程开发中。

单片机 半导体 CMOS 仿真 FPGA Verilog Keil Altera Quartus 相关文章:

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA作为协处理器在实时系统中的应用(04-08)

- 我的FPGA学习历程(05-23)