一种扩频通信调制器的FPGA设计与仿真

时间:11-08

来源:互联网

点击:

1 PN码产生器的功能仿真

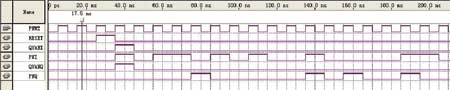

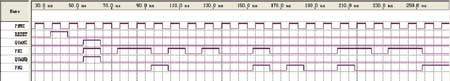

扩频调制器的两路PN码产生器,I路短码的初相是“10,1101,0100”,Q路长码的初相“00,0010,0000,1010,0100”(码初相指两路小M序列初相异或后的初值)。初始的设计见图3。对设计综合过后,进行功能仿真。仿真结果说明:两路PN码起始同步,PNI起始相位:10,1101,0100;PNQ起始相位:00,0010,0000,1010,0100。原始设计符合要求。仿真结果如图4所示。(PNMZ为码钟;RESET为复位信号;PNI、PNQ为I、Q两路PN码;QUANI、QIANQ为I、Q两路PN码全“1”信号。)

图4 两路PN码的功能仿真图

2 PN码产生器的时序仿真

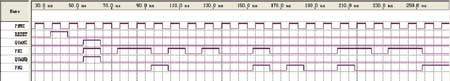

通过功能仿真之后,对设计进行布局布线编译,然后进行时序仿真。发现可能会在PN码序列中产生毛刺信号,并通过多次仿真发现复位信号也可能产生毛刺信号,导致I、Q两路信号起始不同步,如图5所示。

图5 两路PN码的时序仿真图

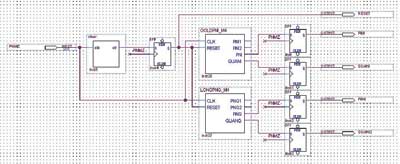

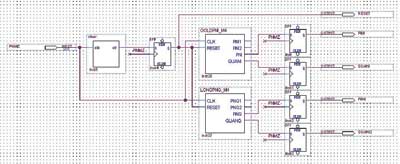

作者对电路进行改进,将复位信号、PN码信号、全“1”信号上加上D触发器,用码钟打一次,消除电路毛刺。改进后的电路如图6所示。

图6 改进后的两路PN码设计图

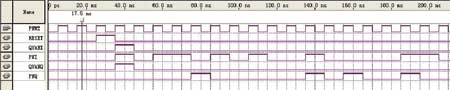

再次进行时序仿真,发现毛刺消除,PN码产生正常,说明两路PN码电路设计正确,可以作为经验证的基本单元加入扩频调制器的FPGA设计。

图7 改进后的PN码时序仿真图

结束语

本文介绍了一种扩频通信调制器的FPGA设计实现方法,着重说明了PN码产生器的设计仿真过程,形象地阐述了FPGA自顶向下的设计思想及详尽的设计流程。FPGA在无线通信工程领域的应用已非常普遍,掌握一种好的设计方法对电子设计师们很重要,希望本文对读者有所帮助。

扩频调制器的两路PN码产生器,I路短码的初相是“10,1101,0100”,Q路长码的初相“00,0010,0000,1010,0100”(码初相指两路小M序列初相异或后的初值)。初始的设计见图3。对设计综合过后,进行功能仿真。仿真结果说明:两路PN码起始同步,PNI起始相位:10,1101,0100;PNQ起始相位:00,0010,0000,1010,0100。原始设计符合要求。仿真结果如图4所示。(PNMZ为码钟;RESET为复位信号;PNI、PNQ为I、Q两路PN码;QUANI、QIANQ为I、Q两路PN码全“1”信号。)

图4 两路PN码的功能仿真图

2 PN码产生器的时序仿真

通过功能仿真之后,对设计进行布局布线编译,然后进行时序仿真。发现可能会在PN码序列中产生毛刺信号,并通过多次仿真发现复位信号也可能产生毛刺信号,导致I、Q两路信号起始不同步,如图5所示。

图5 两路PN码的时序仿真图

作者对电路进行改进,将复位信号、PN码信号、全“1”信号上加上D触发器,用码钟打一次,消除电路毛刺。改进后的电路如图6所示。

图6 改进后的两路PN码设计图

再次进行时序仿真,发现毛刺消除,PN码产生正常,说明两路PN码电路设计正确,可以作为经验证的基本单元加入扩频调制器的FPGA设计。

图7 改进后的PN码时序仿真图

结束语

本文介绍了一种扩频通信调制器的FPGA设计实现方法,着重说明了PN码产生器的设计仿真过程,形象地阐述了FPGA自顶向下的设计思想及详尽的设计流程。FPGA在无线通信工程领域的应用已非常普遍,掌握一种好的设计方法对电子设计师们很重要,希望本文对读者有所帮助。

FPGA 仿真 电子 Verilog EDA 电路图 VHDL 比较器 Quartus 电路 通信工程 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)