利用可编程逻辑实现高性能的罪犯抓捕系统

时间:11-08

来源:互联网

点击:

由于高科技工具成为抓捕罪犯的武器中越来越关键的部分,因此执法机构和安全专业人员不断寻求更快更方便的数据收集和解读方式就不足为奇了。针对这一领域的应用越来越复杂,必须适应不断演变的要求,并把成本控制在机构的有限预算范围之内。鉴于此,具有高性能、灵活性和高成本效益等优势的可编程逻辑(PLD)解决方案无疑是一种理想的解决方案。

两个大学生团队利用FPGA和嵌入式软核处理器开发了两个抓捕罪犯系统的原型,一个是带无线自动追踪摄像机的警车支持系统,一个是防止安全系统被突破的指纹识别系统。

盯住可疑对象不放-即使是高速情况下

当追踪行动启动时,警官只有很短的时间用来激活警笛、向控制中心作汇报并与其他巡逻队通信。由于这些事情的发生几乎是同时的,因此警官还依赖于车辆追踪系统把逃跑的犯罪分子锁定在视距内。然而,当疑犯在拥挤的交通中急速穿越时,采用固定位置摄像机的传统追踪系统很容易失去他们的踪迹。因此将需要这样一种车载系统:它能时刻盯住可疑车辆,同时让警官与现场及总部的同事共享和接收信息。

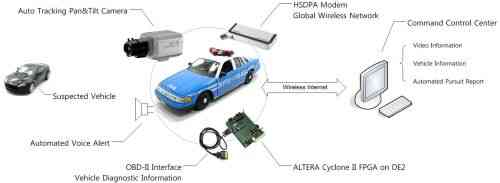

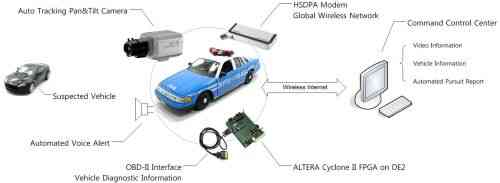

图1:设计理念。

韩国仁荷/弘益航空航天大学的学生开发出的板载警用车辆支持系统原型,该集成解决方案包含以下几个组件:

· 无线自动追踪系统:可持续追踪可疑车辆,将车辆的图像显示在显示器中心。一部全方向移动的摄像机使用FPGA控制的步进电机实现上下左右的移动,可以通过快速反应捕获快速行进的车辆。

· 自动语音告警系统:使用嵌入式处理器来实现MPEG音频解码,用于向逃跑疑犯发出警告。

· HSDPA功能:提供实时数据和图像共享。

· 基于FPGA的连接板载诊断系统(OBD-II)的接口:用于监视警用车辆的发动机性能参数。

FPGA和嵌入式处理器的有机结合使该系统很容易实现图像、语音、图像和数据处理。

在单系统中实现语音、视频和数据

在技术平台方面,设计团队使用了Altera的DE2开发和教学板,这种板包含了Cyclone II FPGA、Quartus II设计软件和Nios II嵌入式处理器。

单个Cyclone II FPGA支持整个系统的运行,可以完成图像处理、压缩、数据传送、MPEG音频解码、电机控制和OBD通信等功能。所有必要的组件都利用SOPC Builder系统设计工具装配在一起,从而允许设计团队设计一个模块,并可以经过修改用于或直接复用于其他应用。

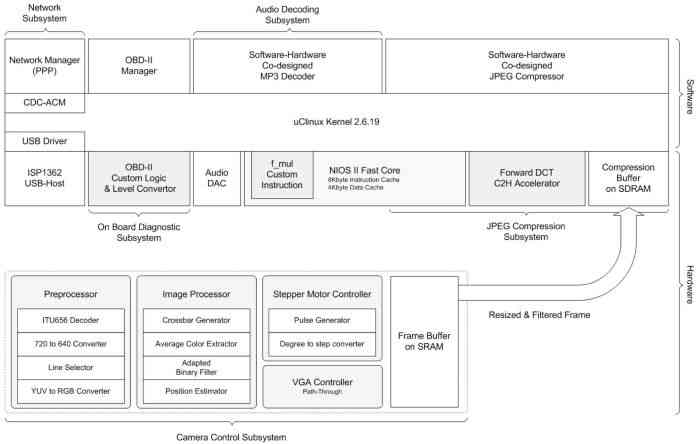

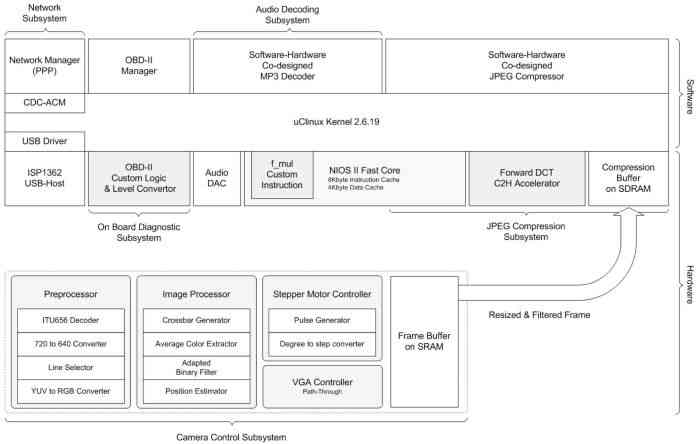

图2:自动追踪系统的架构。

自动追踪摄像机

摄像机的图像处理模块将全方位移动命令传送给FPGA上的系统步进电机控制器。根据这样的命令,步进电机控制器可以产生操作信号脉冲,然后将这些信号发送给每个电机。

摄像机的图像捕捉模块将模拟图像信息转换成DE2板上的ITU656标准数字流,并使用该数据流:控制自动追踪摄像机的左、右、上、下操作;支持视像共享系统和JPEG压缩的无线传送;提供车载显示。

当警官需要启动摄像机的追踪模式时,只需将摄像机对准目标车辆,并按下DE2板上的一个按键。接着由同样在FPGA上运行的图像处理模块从目标车辆中提取平均颜色,并估计其位置。一旦车辆开始移动,全方位移动摄像机就开始对它进行追踪。该系统每隔30分之一秒就向电机控制器传送一次控制命令,速度是它的关键优势之一。捕获到的图像被存储在USB存储设备中,同时传送给警局命令中心。当然,追踪模式只适用于白天。

实时JPEG压缩通常要求高性能DSP芯片或ASSP。在这个情况下,设计团队使用Nios II C到硬件的加速编译器(C2H)执行libjpeg前向离散余弦变换(DCT)函数来满足性能目标要求,而不需要外部处理器或DSP芯片。C2H编译器可以将时间关键的ANSI C函数转换成FPGA中的硬件加速器,从而提升它们的性能。

图3:实现自动追踪系统的原理框图。

自动语音警告

当车辆的自动追踪摄像机开始工作在追踪模式时,会触发自动语音警告功能打开,并向逃跑疑犯发出警告。在DE2板上100MHz的嵌入式处理器用于播放MPEG音频数据的定制指令集。最初回放性能是个问题,但通过在Nios II软核处理器中增加64位乘法定制指令,设计团队将性能提高了2.5倍。

定制的OBD-II接口

连接OBD-II的接口不仅贯通了汽车电子设备之间的通信,而且也将诊断工具连接到发动机控制单元(ECU),实现汽车维护和监视。SOPC Builder UART组件连接到OBD-II接口,用于收集车辆行驶速度、燃油状态和车辆故障状态等信息。

因此,设计团队能够利用Nios II定制指令的性能优势和C到硬件的加速功能创建一个高性能系统,为现场警察提供帮助。由于使用了FPGA,团队可以灵活地根据需要提升性能,不需要增加时钟频率和降低功耗,也无需采用高速设计。当团队遇到要求修改硬件设计的性能问题时,他们只需重新编程FPGA就能应对这些变化。

两个大学生团队利用FPGA和嵌入式软核处理器开发了两个抓捕罪犯系统的原型,一个是带无线自动追踪摄像机的警车支持系统,一个是防止安全系统被突破的指纹识别系统。

盯住可疑对象不放-即使是高速情况下

当追踪行动启动时,警官只有很短的时间用来激活警笛、向控制中心作汇报并与其他巡逻队通信。由于这些事情的发生几乎是同时的,因此警官还依赖于车辆追踪系统把逃跑的犯罪分子锁定在视距内。然而,当疑犯在拥挤的交通中急速穿越时,采用固定位置摄像机的传统追踪系统很容易失去他们的踪迹。因此将需要这样一种车载系统:它能时刻盯住可疑车辆,同时让警官与现场及总部的同事共享和接收信息。

图1:设计理念。

韩国仁荷/弘益航空航天大学的学生开发出的板载警用车辆支持系统原型,该集成解决方案包含以下几个组件:

· 无线自动追踪系统:可持续追踪可疑车辆,将车辆的图像显示在显示器中心。一部全方向移动的摄像机使用FPGA控制的步进电机实现上下左右的移动,可以通过快速反应捕获快速行进的车辆。

· 自动语音告警系统:使用嵌入式处理器来实现MPEG音频解码,用于向逃跑疑犯发出警告。

· HSDPA功能:提供实时数据和图像共享。

· 基于FPGA的连接板载诊断系统(OBD-II)的接口:用于监视警用车辆的发动机性能参数。

FPGA和嵌入式处理器的有机结合使该系统很容易实现图像、语音、图像和数据处理。

在单系统中实现语音、视频和数据

在技术平台方面,设计团队使用了Altera的DE2开发和教学板,这种板包含了Cyclone II FPGA、Quartus II设计软件和Nios II嵌入式处理器。

单个Cyclone II FPGA支持整个系统的运行,可以完成图像处理、压缩、数据传送、MPEG音频解码、电机控制和OBD通信等功能。所有必要的组件都利用SOPC Builder系统设计工具装配在一起,从而允许设计团队设计一个模块,并可以经过修改用于或直接复用于其他应用。

图2:自动追踪系统的架构。

自动追踪摄像机

摄像机的图像处理模块将全方位移动命令传送给FPGA上的系统步进电机控制器。根据这样的命令,步进电机控制器可以产生操作信号脉冲,然后将这些信号发送给每个电机。

摄像机的图像捕捉模块将模拟图像信息转换成DE2板上的ITU656标准数字流,并使用该数据流:控制自动追踪摄像机的左、右、上、下操作;支持视像共享系统和JPEG压缩的无线传送;提供车载显示。

当警官需要启动摄像机的追踪模式时,只需将摄像机对准目标车辆,并按下DE2板上的一个按键。接着由同样在FPGA上运行的图像处理模块从目标车辆中提取平均颜色,并估计其位置。一旦车辆开始移动,全方位移动摄像机就开始对它进行追踪。该系统每隔30分之一秒就向电机控制器传送一次控制命令,速度是它的关键优势之一。捕获到的图像被存储在USB存储设备中,同时传送给警局命令中心。当然,追踪模式只适用于白天。

实时JPEG压缩通常要求高性能DSP芯片或ASSP。在这个情况下,设计团队使用Nios II C到硬件的加速编译器(C2H)执行libjpeg前向离散余弦变换(DCT)函数来满足性能目标要求,而不需要外部处理器或DSP芯片。C2H编译器可以将时间关键的ANSI C函数转换成FPGA中的硬件加速器,从而提升它们的性能。

图3:实现自动追踪系统的原理框图。

自动语音警告

当车辆的自动追踪摄像机开始工作在追踪模式时,会触发自动语音警告功能打开,并向逃跑疑犯发出警告。在DE2板上100MHz的嵌入式处理器用于播放MPEG音频数据的定制指令集。最初回放性能是个问题,但通过在Nios II软核处理器中增加64位乘法定制指令,设计团队将性能提高了2.5倍。

定制的OBD-II接口

连接OBD-II的接口不仅贯通了汽车电子设备之间的通信,而且也将诊断工具连接到发动机控制单元(ECU),实现汽车维护和监视。SOPC Builder UART组件连接到OBD-II接口,用于收集车辆行驶速度、燃油状态和车辆故障状态等信息。

因此,设计团队能够利用Nios II定制指令的性能优势和C到硬件的加速功能创建一个高性能系统,为现场警察提供帮助。由于使用了FPGA,团队可以灵活地根据需要提升性能,不需要增加时钟频率和降低功耗,也无需采用高速设计。当团队遇到要求修改硬件设计的性能问题时,他们只需重新编程FPGA就能应对这些变化。

FPGA 嵌入式 显示器 步进电机 Altera Quartus USB DSP 汽车电子 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)