基于CPLD控制的直流固态功率控制器的设计

时间:11-07

来源:互联网

点击:

5 试验结果

该仿真是在ALTERA系列CPLD的开发环境MAX+PLUS II上进行的。当在不同的电流值下采集到的四路SSPC负载电流为不同值时,SSPC的工作情况也不一样。

(1) 当I/Iopr8时,SSPC立即跳闸。

(2) 当I/Iopr为1.2(SSPC_1)、2(SSPC_2)、由1.2增加到2(SSPC_3)和5(SSPC_4)时,SSPC的跳闸时间分别为402ms、161ms、223ms和26ms。

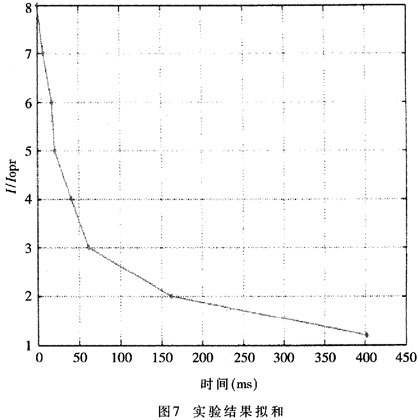

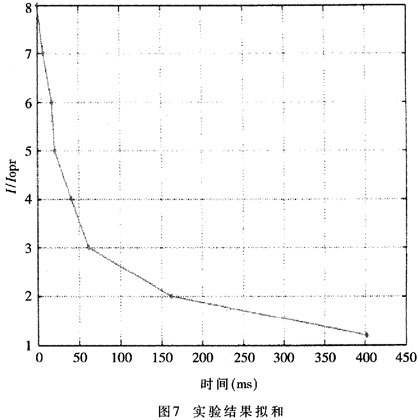

各个临界点的实验所得数据经过曲线拟和,得到如图7所示结果。

试验结果表明,利用CPLD进行SSPC的开发设计,其延迟时间完全可以通过编程控制,且各路SSPC之间干扰较少。

CPLD内部的硬件结构决定了系统良好的抗干扰性和高可靠性,非常适合于电力系统方面的控制。因此,采用CPLD应是一个研究方向。

该仿真是在ALTERA系列CPLD的开发环境MAX+PLUS II上进行的。当在不同的电流值下采集到的四路SSPC负载电流为不同值时,SSPC的工作情况也不一样。

(1) 当I/Iopr8时,SSPC立即跳闸。

(2) 当I/Iopr为1.2(SSPC_1)、2(SSPC_2)、由1.2增加到2(SSPC_3)和5(SSPC_4)时,SSPC的跳闸时间分别为402ms、161ms、223ms和26ms。

各个临界点的实验所得数据经过曲线拟和,得到如图7所示结果。

试验结果表明,利用CPLD进行SSPC的开发设计,其延迟时间完全可以通过编程控制,且各路SSPC之间干扰较少。

CPLD内部的硬件结构决定了系统良好的抗干扰性和高可靠性,非常适合于电力系统方面的控制。因此,采用CPLD应是一个研究方向。

半导体 电路 CPLD CMOS 电流 电阻 电压 MOSFET LTE 放大器 滤波器 VHDL 仿真 相关文章:

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA 上同步开关噪声的分析(04-05)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)