基于CPLD的片内振荡器设计

时间:11-07

来源:互联网

点击:

3 电路仿真及测试结果

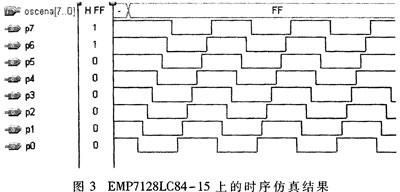

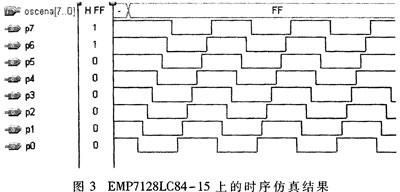

本文以Altera公司的MAX+plus II 10.2为设计工具,在MAX7000S系列芯片上实现并测试。图3为选用EMP7128LC84-15芯片的时序仿真结果。其中p0~p7分别为环形振荡电路中单个门之后的电路节点;oscena[7…0]为各延时门电路的控制端(即所有二输入门中多余的输入端)。

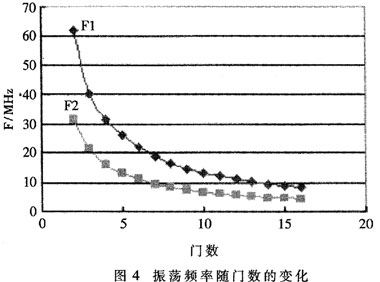

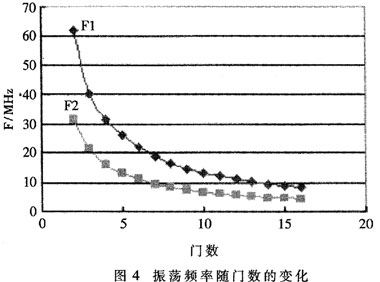

表1列出了以EPM7128LC84-15为目标芯片、采用Tektronic TDS2012示波器对用不同门数实现的片内振荡器的测试数据。F1和F2分别表示片内振荡器输出和二分频输出的测量数据。图4给出了测量数据的曲线。

表1数据表明,通过增加门电路的数量可以有规律地减小振荡电路的工作频率,由每个逻辑单元实现的门电路单元延时tpd在7.5~10ns之间。

本文介绍的基于CPLD的片内振荡器设计方法,在改变该振荡器电路中门电路数量时,可以有规律地将振荡频率控制在8MHz~62MHz范围内。振荡器的片内设计使基于CPLD的片上系统(SoC)设计无需外接时钟信号源,加大了系统的集成度并降低了设计成本。本方法有很大的通用性,可以方便地在不同CPLD芯片间移植。仿真和测试数据表明该设计方法具有正确性和可行性。

本文以Altera公司的MAX+plus II 10.2为设计工具,在MAX7000S系列芯片上实现并测试。图3为选用EMP7128LC84-15芯片的时序仿真结果。其中p0~p7分别为环形振荡电路中单个门之后的电路节点;oscena[7…0]为各延时门电路的控制端(即所有二输入门中多余的输入端)。

表1列出了以EPM7128LC84-15为目标芯片、采用Tektronic TDS2012示波器对用不同门数实现的片内振荡器的测试数据。F1和F2分别表示片内振荡器输出和二分频输出的测量数据。图4给出了测量数据的曲线。

表1数据表明,通过增加门电路的数量可以有规律地减小振荡电路的工作频率,由每个逻辑单元实现的门电路单元延时tpd在7.5~10ns之间。

本文介绍的基于CPLD的片内振荡器设计方法,在改变该振荡器电路中门电路数量时,可以有规律地将振荡频率控制在8MHz~62MHz范围内。振荡器的片内设计使基于CPLD的片上系统(SoC)设计无需外接时钟信号源,加大了系统的集成度并降低了设计成本。本方法有很大的通用性,可以方便地在不同CPLD芯片间移植。仿真和测试数据表明该设计方法具有正确性和可行性。

振荡器 电路 FPGA CPLD 集成电路 电压 Altera Quartus 仿真 SoC 电子 自动化 EDA CMOS 半导体 示波器 相关文章:

- 数字下变频的FPGA实现(05-12)

- 基于FPGA的任意时延伪码序列产生方法(04-12)

- 在嵌入式设计中降低CPLD的功耗(04-30)

- Actel数模结合FPGA的远程控制器设计(05-13)

- 基于FPGA的相检宽带测频系统的设计(06-08)

- ACEX 1K系列CPLD配置方法探讨(06-09)