CPLD在信号滤波和抗干扰中的应用

时间:10-20

来源:互联网

点击:

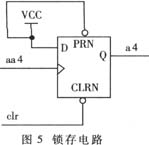

当aa4为由低变高时,a4变为高电平。由clr信号清零。

2.3 按键消抖及数据输出

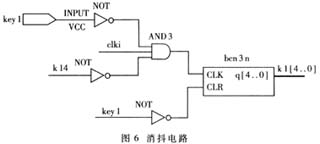

按键的消抖也通过计数器来实现,电路原理图如图6所示。

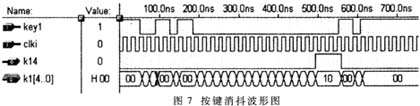

按键未按下时为高电平,封锁时钟信号。按键按下时,计数器开始计数。当计数器输出最高位为"1"时,亦封锁时钟信号,防止按键时间不定使需要的k14信号不定。当按键信号为高电平时,对计数器清零,防止计数器累加干扰信号而造成误动作。波形如图7所示。

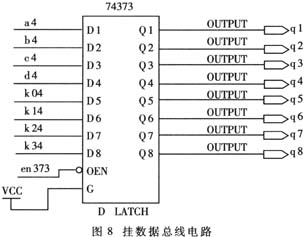

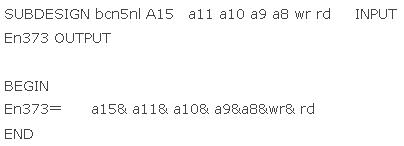

泵冲和按键经处理后的信号a4、b4、c4、d4、k04、k14、k24、k34,经74373挂于数据总线,如图8所示。74373使能信号由图9电路产生。

它采用文本编辑,具体如下:

若单片机发出读81XXH地址中数的信号,则选通此373,读出其数。

以上介绍了采用CPLD实现数字滤波及抗干扰。该设计已在产品开发中成功应用,效果良好,达到了预期的目的。前面我们已经提到,一个传统的设计,往往在软件滤波和硬件滤波两者的优缺点之间寻找一个平衡点。用我们通常的成语来讲,这样做可以说是扬长避短或取长补短。一直以来,我们都把这两个成语看成是褒义的,不过细细品味一下其中的韵味似乎并不完全是好的代表:发扬长处固然值得称道,但回避短处未必是解决问题的最佳途径,毕竟回避并不能解决问题的本质,哪怕是取其长处来弥补短处,也不是长远出路。应该直接去克服掉短处为佳。采用CPLD则可将软硬件滤波的优点兼而有之,同时将它们的缺点摒弃,从而达到扬长去短的目的。用CPLD实现滤波只占用较少的资源,故可用其实现其它数字电路,同时实现滤波。

单片机 传感器 电路 继电器 CPLD 滤波器 总线 相关文章:

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA作为协处理器在实时系统中的应用(04-08)

- 我的FPGA学习历程(05-23)