CVSD算法分析及其在FPGA中的实现

时间:10-15

来源:互联网

点击:

3.3 CVSD算法的仿真

以正弦单音输入信号为例,利用信号源产生信号幅度O.5 Vpp,频率fin(t)=1 kHz的正弦信号作为测试信号,在FPGA中利用高倍时钟产生fs(t)=64 kHz的采样时钟。对输入A/D的音频信号采用专用低通滤波芯片进行了滤波。D/A输出的信号包含了许多不必要的高次谐波分量,因此也采用低通滤波器对其进行了平滑滤波。

在设计上,不仅仅是采用FPGA实现和验证自己的CVSD编译码算法,还和专用芯片CMX639进行互相通信进行验证。CMX639是一款CVSD全双工音频调制芯片,集成了编码和译码功能,实现了单芯片语音处理能力,外围设备简单,用户可以根据实际情况,自主选择采样速率。

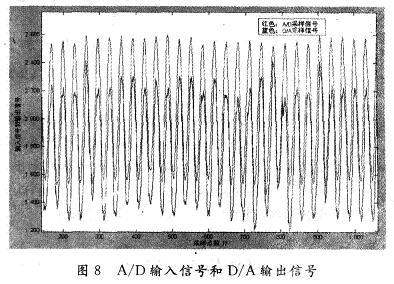

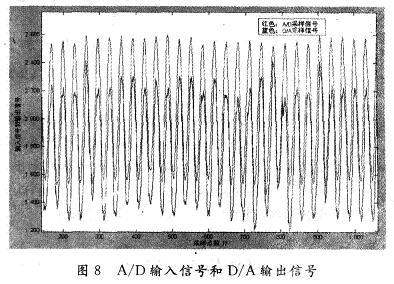

图8是通过ChipScope Pro采集的实时正弦信号。从图中可以看出量阶△的大小能够很好地反映输入信号斜率的大小,输出端输出信号能够很好地重现输入信号,说明CVSD编译码方式是有效的。

3.4 CVSD算法的实现

采用原理图和VHDL语言相结合的方式在FPGA中实现了CVSD电路。具体实现步骤如下:

(1)根据算法框图设计顶层原理图CVSD.SCH;

(2)利用IP Core产生底层所需要的乘法器;

(3)利用VHDL语言完成CVSD编译码模块;

(4)I/O管脚定义,约束条件编写;

(5)设计综合、编译;

(6)bit文件生成、下载,通过ChipScope Pro进行仿真测试;

(7)根据仿真测试结果返回修改设计,直到设计成功;

(8)mcs文件生成、加载,最终验证。

验证是FPGA设计中很重要的一环,只有通过验证才能说明设计的正确与否。采用XILINX公司的Spartan一3系列中的XC3S1500来具体实现CVSD的编译码功能。通过自己设计的编译码算法和CMX639专用芯片的编译码模块互相通信,输入实际语音信号测试,能够很好地从D/A输出语音信号,从CMX639译码输出也能听到语音信号,达到了满意的效果。

4 结 语

本文提出的FPGA设计方法很好地实现了CVSD编译码功能,充分利用了FPGA的优势,可以同时实现多路CVSD编译码功能,弥补了采用专用芯片实现CVSD编译码的不足,设计灵活、简单,成本低,具有很好的应用前景。

以正弦单音输入信号为例,利用信号源产生信号幅度O.5 Vpp,频率fin(t)=1 kHz的正弦信号作为测试信号,在FPGA中利用高倍时钟产生fs(t)=64 kHz的采样时钟。对输入A/D的音频信号采用专用低通滤波芯片进行了滤波。D/A输出的信号包含了许多不必要的高次谐波分量,因此也采用低通滤波器对其进行了平滑滤波。

在设计上,不仅仅是采用FPGA实现和验证自己的CVSD编译码算法,还和专用芯片CMX639进行互相通信进行验证。CMX639是一款CVSD全双工音频调制芯片,集成了编码和译码功能,实现了单芯片语音处理能力,外围设备简单,用户可以根据实际情况,自主选择采样速率。

图8是通过ChipScope Pro采集的实时正弦信号。从图中可以看出量阶△的大小能够很好地反映输入信号斜率的大小,输出端输出信号能够很好地重现输入信号,说明CVSD编译码方式是有效的。

3.4 CVSD算法的实现

采用原理图和VHDL语言相结合的方式在FPGA中实现了CVSD电路。具体实现步骤如下:

(1)根据算法框图设计顶层原理图CVSD.SCH;

(2)利用IP Core产生底层所需要的乘法器;

(3)利用VHDL语言完成CVSD编译码模块;

(4)I/O管脚定义,约束条件编写;

(5)设计综合、编译;

(6)bit文件生成、下载,通过ChipScope Pro进行仿真测试;

(7)根据仿真测试结果返回修改设计,直到设计成功;

(8)mcs文件生成、加载,最终验证。

验证是FPGA设计中很重要的一环,只有通过验证才能说明设计的正确与否。采用XILINX公司的Spartan一3系列中的XC3S1500来具体实现CVSD的编译码功能。通过自己设计的编译码算法和CMX639专用芯片的编译码模块互相通信,输入实际语音信号测试,能够很好地从D/A输出语音信号,从CMX639译码输出也能听到语音信号,达到了满意的效果。

4 结 语

本文提出的FPGA设计方法很好地实现了CVSD编译码功能,充分利用了FPGA的优势,可以同时实现多路CVSD编译码功能,弥补了采用专用芯片实现CVSD编译码的不足,设计灵活、简单,成本低,具有很好的应用前景。

FPGA 电路 滤波器 编码器 低通滤波器 电路图 VHDL 仿真 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)