LS码及其FPGA的实现

时间:10-12

来源:互联网

点击:

3 FPGA的下载测试

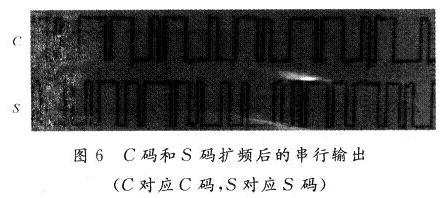

完成了设计输入和仿真后,就可以进行FPGA的下载测试,所针对的是基于Xilinx Spartan2S-300E的FPGA芯片的硬件环境。图6~图8是使用FLUKE199C型示波器观测到的波形。其中,图6是C码和S码分别扩频后的串行模块serial_out输出,图中的每一虚线单元格对应10 μs,可以粗略算出此时的串行速率大约为1 Mb/s,与所需1.024 Mb/s基本吻合。

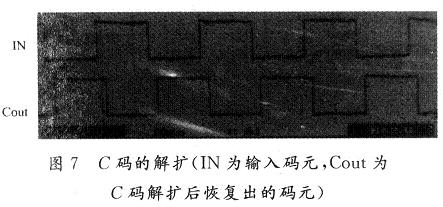

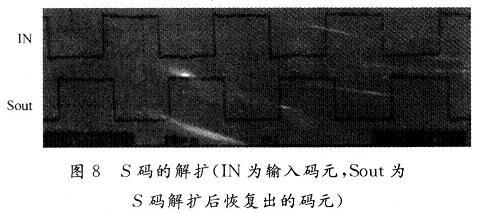

图7和图8分别是C码和S码解扩后的输出与原始的数据码元IN的比较,可以大致估算出Cout和Sout的数据速率大约为64 Kb/s,测试结果表明所设计正确,硬件平台运行稳定。

4 结 语

本文通过对LS码在FPGA中的实现进行了研究,介绍了LS码的构造和相关性,主要介绍了LS码构造的算法验证,FPGA的设计输入、仿真以及下载测试,仿真和测试的结果表明所设计的输出正确,达到了预期的目的。今后的工作主要包括LS码在FPGA中的调制、解调、同步等算法的实现。

完成了设计输入和仿真后,就可以进行FPGA的下载测试,所针对的是基于Xilinx Spartan2S-300E的FPGA芯片的硬件环境。图6~图8是使用FLUKE199C型示波器观测到的波形。其中,图6是C码和S码分别扩频后的串行模块serial_out输出,图中的每一虚线单元格对应10 μs,可以粗略算出此时的串行速率大约为1 Mb/s,与所需1.024 Mb/s基本吻合。

图7和图8分别是C码和S码解扩后的输出与原始的数据码元IN的比较,可以大致估算出Cout和Sout的数据速率大约为64 Kb/s,测试结果表明所设计正确,硬件平台运行稳定。

4 结 语

本文通过对LS码在FPGA中的实现进行了研究,介绍了LS码的构造和相关性,主要介绍了LS码构造的算法验证,FPGA的设计输入、仿真以及下载测试,仿真和测试的结果表明所设计的输出正确,达到了预期的目的。今后的工作主要包括LS码在FPGA中的调制、解调、同步等算法的实现。

FPGA 无线电 SoC 仿真 Verilog ModelSim 总线 Xilinx 示波器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)