用中档FPGA实现多相滤波器

时间:10-08

来源:互联网

点击:

利用多相FIR滤波器进行内插

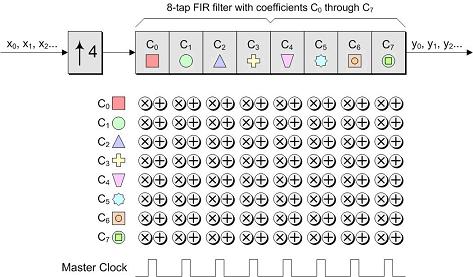

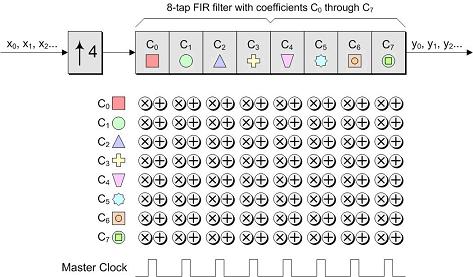

现在让我们来考虑内插的情况。首先让我们先考虑一个基于常规8抽头FIR滤波器的内插子系统的符号表示,如图15所示。

图15传统的基于8抽头FIR滤波器的内插器的符号表示

针对这些例子的用途,我们假设内插因子为L = 4,主时钟频率为FHz。正如先前所讨论的,向上采样(插入零值样本的过程)发生在滤波操作之前。

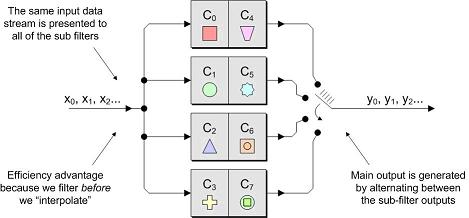

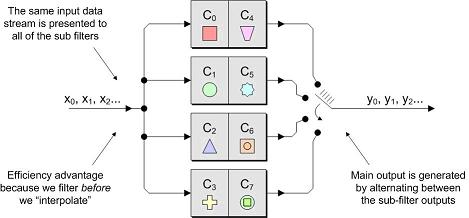

现在让我们来考虑一个最初的多相实现,我们原来的8抽头FIR滤波器被分成四个2 抽头子滤波器,如图16所示。

图16 基于4 × 2抽头多相滤波器的内插器的符号表示

在这种情况下,相同的输入数据流面向所有的四个子滤波器,在子滤波器输出之间轮流产生主输出数据流。最终的结果是,多相实现含有如同我们的常规8抽头FIR滤波器相同数量的乘法器和加法器。然而,因为在内插之前进行了滤波,子滤波器只需要以1 / 4的主时钟频率运行,从而大大节省了功耗(这里主时钟用于子滤波器输出之间的采样)。

此外,多相实现不需要向上采样(零值插入)的逻辑。当然,我们可以用完全运行于主时钟频率和复用系数的单个2抽头子滤波器取代原来的多相滤波器实现。

内插实现的这些例子的总结见表2 。

表2内插实现实例的总结

总结

DSP设计人员的工具箱的支柱之一是有限脉冲响应( FIR )滤波器。FIR滤波器越长(有大量的抽头),滤波器的响应越好。但是更多的抽头增加了逻辑要求、增加了计算的复杂性,增加了功耗,以及有更大可能的饱和/溢出。

多相技术3可用于实现滤波器,提供可比较的结果,而使用较少的逻辑,需要更少的计算资源、消耗更低的功率,并减少了可能的饱和/溢出。

所有这一切都意味着,多相基于滤波器的抽取器、内插器和重采样功能是非常适合用更小的中档FPGA来实现,如Lattice半导体公司的拥有SERDES功能的LatticeECP3系列,它具有高性能的sysDSP模块。它的特点是有dual-slice结构,具有级联/链接DSP slice和模块的功能,增强的DSP指令集使LatticeECP3系列能够引人注目地用于范围广泛的数字信号处理的应用,包括那些需要传统的FIR和基于多相的滤波功能。

注释:

1 DSP的插值形式不同于传统的数学插值方法,从现有的数据点构建新的数据点,但它的概念是相同的,因为它涉及到从现有的值产生新的值。

2 显然,在第一个抽头与0 (零)相加可以省略。然而在实践中,由MAC实行每对加和乘的操作,因此即使我们与0相加,逻辑仍然存在。

3 应该指出的是,本文对多相滤波器专题只提供一个高层次的介绍;文中的例子都做了简化。

现在让我们来考虑内插的情况。首先让我们先考虑一个基于常规8抽头FIR滤波器的内插子系统的符号表示,如图15所示。

图15传统的基于8抽头FIR滤波器的内插器的符号表示

针对这些例子的用途,我们假设内插因子为L = 4,主时钟频率为FHz。正如先前所讨论的,向上采样(插入零值样本的过程)发生在滤波操作之前。

现在让我们来考虑一个最初的多相实现,我们原来的8抽头FIR滤波器被分成四个2 抽头子滤波器,如图16所示。

图16 基于4 × 2抽头多相滤波器的内插器的符号表示

在这种情况下,相同的输入数据流面向所有的四个子滤波器,在子滤波器输出之间轮流产生主输出数据流。最终的结果是,多相实现含有如同我们的常规8抽头FIR滤波器相同数量的乘法器和加法器。然而,因为在内插之前进行了滤波,子滤波器只需要以1 / 4的主时钟频率运行,从而大大节省了功耗(这里主时钟用于子滤波器输出之间的采样)。

此外,多相实现不需要向上采样(零值插入)的逻辑。当然,我们可以用完全运行于主时钟频率和复用系数的单个2抽头子滤波器取代原来的多相滤波器实现。

内插实现的这些例子的总结见表2 。

表2内插实现实例的总结

总结

DSP设计人员的工具箱的支柱之一是有限脉冲响应( FIR )滤波器。FIR滤波器越长(有大量的抽头),滤波器的响应越好。但是更多的抽头增加了逻辑要求、增加了计算的复杂性,增加了功耗,以及有更大可能的饱和/溢出。

多相技术3可用于实现滤波器,提供可比较的结果,而使用较少的逻辑,需要更少的计算资源、消耗更低的功率,并减少了可能的饱和/溢出。

所有这一切都意味着,多相基于滤波器的抽取器、内插器和重采样功能是非常适合用更小的中档FPGA来实现,如Lattice半导体公司的拥有SERDES功能的LatticeECP3系列,它具有高性能的sysDSP模块。它的特点是有dual-slice结构,具有级联/链接DSP slice和模块的功能,增强的DSP指令集使LatticeECP3系列能够引人注目地用于范围广泛的数字信号处理的应用,包括那些需要传统的FIR和基于多相的滤波功能。

注释:

1 DSP的插值形式不同于传统的数学插值方法,从现有的数据点构建新的数据点,但它的概念是相同的,因为它涉及到从现有的值产生新的值。

2 显然,在第一个抽头与0 (零)相加可以省略。然而在实践中,由MAC实行每对加和乘的操作,因此即使我们与0相加,逻辑仍然存在。

3 应该指出的是,本文对多相滤波器专题只提供一个高层次的介绍;文中的例子都做了简化。

电子 DSP 滤波器 FPGA 低通滤波器 半导体 相关文章:

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)