FPGA重复配置和测试的实现

时间:10-09

来源:互联网

点击:

从制造的角度来讲,FPGA测试是指对FPGA器件内部的逻辑块、可编程互联线、输入输出块等资源的检测。完整的FPGA测试包括两步,一是配置FPGA、然后是测试FPGA,配置FPGA是指将FPGA通过将配置数据下载编程使其内部的待测资源连接成一定的结构,在尽可能少的配置次数下保证FPGA内部资源的测试覆盖率,配置数据称为TC,配置FPGA的这部分时间在整个测试流程占很大比例;测试FPGA则是指对待测FPGA施加设计好的测试激励并回收激励,测试激励称为TS。

通常来说,要完成FPGA内部资源的完整测试需要针对不同的待测资源设计多种配置图形,多次下载到FPGA,反复施加激励和回收测试响应,通过对响应数据的分析来诊断故障。因此,用于FPGA测试的仪器或系统的关键技术在于:如何加快单次配置的时间,以节省测试过程中的配置时间开销;如何实现自动重复配置和测试,将FPGA较快速度的在线配置和快速测试结合起来。

由于一般的集成电路自动测试仪ATE为通用IC测试设计,但FPGA测试有上述特殊性,在芯片功能测试之前必须对其进行特定的配置,否则芯片是不具备内部电路结构的,内部资源将无法测试,而通用的ATE要完成测试步骤中的配置功能时,需要以人工或通过电脑专门编程修改配置数据生成测试系统可执行的测试激励形式进行配置,且如果配置数据较多,这个转换过程将可能比较复杂,易用性不强,无法高效地用于FPGA器件的测试中,需要对FPGA测试设计专用的测试平台以满足其配置测试需求。

我们设计的系统实现了快速重复配置和测试的功能,配置数据可以直接引用EDA软件生成的位流文件而不需要像ATE一样转换成繁杂的测试激励形式,相较于ATE有一定的优势,对FPGA测试有一定的使用价值。

FPGA可重复配置和测试系统结构概述

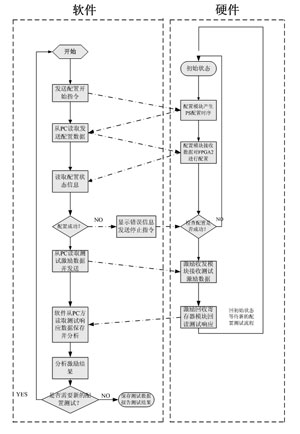

系统框图如图1所示。

图1 可重复配置测试系统结构框图

系统功能的实现包括软件和硬件两部分。硬件部分包含PCI桥接芯片、FPGA1中的数据接口模块、配置模块、测试模块和被测FPGA。软件部分包含对实现FPGA配置部分的代码和实现FPGA测试部分的代码。FPGA1中的各硬件模块通过EDA软件以JTAG接口固化FPGA1中,其中FPGA1中的配置模块负责接收来自PC方软件发送的配置数据,并产生对被测FPGA的配置时序,完成配置步骤,测试模块负责发送测试激励和回收被测FPGA的响应数据,等待PC方软件的回收。

系统软硬件交互流程

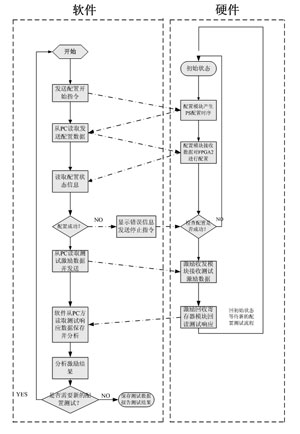

整个系统通过软硬件的数据交互实现对被测FPGA的自动配置和测试的流程,软硬件交互的流程从图2可以体现:系统启动后,首先需要开始对被测FPGA进行数据配置,由软件向硬件发送配置开始指令,硬件接收指令后对被测FPGA产生配置开始的时序,告诉被测FPGA准备接收配置数据。当软件查询到配置模块中的状态寄存器值代表等待数据时开始发送配置数据。配置数据发送完成后,软件通过读取配置模块的状态寄存器值判断配置是否成功,决定是否可以开始测试。如果配置成功,软件则开始向被测FPGA发送测试激励数据并读回测试响应保存在电脑中,由软件对测试响应进行分析决定是否需要进行下一次配置和测试流程。如果需要,在一定的延时之后软硬件将回复初始状态,并选择新的配置数据和测试数据,开始新一轮的配置后测试流程。

图2 FPGA芯片自动重复下载自动测试系统软硬件交互流程图

软硬件数据交互的通路是PCI总线,软件向FPGA1发送指令或数据时,软件通过PCI应用编程接口函数将数据放到PCI总线上,PCI桥接芯片将较为复杂的PCI接口信号转化为相对简单的Local Bus数据信号,由FPGA1中的接口模块接收并产生相应的动作。而软件向FPGA1读取数据的通路则相反。图3和图4分别是软件在VC++6.0环境中断点调试发送指令和软件向FPGA1发送指令时由嵌入式逻辑分析仪SignalTAP II捕捉到的指令数据和接口模块波形。

图3 VC++6.0环境中断点调试指令发送

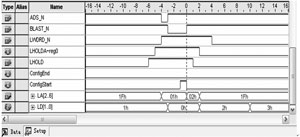

图4 嵌入式逻辑分析仪SignalTAP II波形

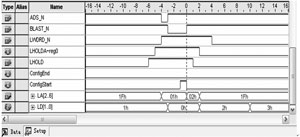

图4中ADS_N、BLAST_N、LWORD_N、LHOLD、LHOLDA是Local Bus的接口信号,ConfigEnd和ConfigStart是分别代表配置结束和配置开始的标志寄存器,LA是接口的地址信号,用于模块中控制寄存器的寻址,LD是接口的数据信号,用于指令数据的发送和数据的回收。

以配置开始指令的发送为例,从图3图4两图中可以看出软硬件交互过程中的指令发送方式,在VC++中单步调试,发送一个开始指令0x01到配置命令寄存器地址0x01,通过硬件模块的接口动作,用嵌入式存储器SignalTap II中捕捉到LA的数据为1h,LD上的数据为1h后ConfigStart寄存器置高,配置开始。

配置速度测试实验

软硬件具体方案设计完毕后,软件在Visual C++6.0环境下实现并调试。硬件在QuartusII7.1软件下编译。

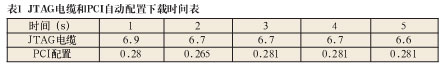

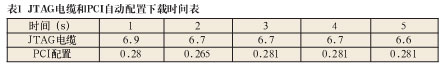

为了对比基于PCI总线的FPGA高速配置方案与基于ByteBlasterII JTAG下载电缆的速度性能,首先使用QuartusII7.1软件采用JTAG方式对FPGA2配置5次,计算每次下载所示时间,得到如表1中所示的数据;再使用本系统中基于PCI总线的配置功能对FPGA2配置5次,软件会自行计算总的下载时间,得到如表1中所示的数据:

从表1的数据对比中可以看到,基于PCI总线的自动下载配置方式要比基于JTAG电缆的下载配置方式提高超过20倍的速度,如果使用基于JTAG电缆对某大容量的FPGA下载需要近20分钟的话,使用PCI下载方式则只需不到1分钟的下载时间,具有明显的速度优势,大大节省了FPGA测试中的数据配置时间。

通常来说,要完成FPGA内部资源的完整测试需要针对不同的待测资源设计多种配置图形,多次下载到FPGA,反复施加激励和回收测试响应,通过对响应数据的分析来诊断故障。因此,用于FPGA测试的仪器或系统的关键技术在于:如何加快单次配置的时间,以节省测试过程中的配置时间开销;如何实现自动重复配置和测试,将FPGA较快速度的在线配置和快速测试结合起来。

由于一般的集成电路自动测试仪ATE为通用IC测试设计,但FPGA测试有上述特殊性,在芯片功能测试之前必须对其进行特定的配置,否则芯片是不具备内部电路结构的,内部资源将无法测试,而通用的ATE要完成测试步骤中的配置功能时,需要以人工或通过电脑专门编程修改配置数据生成测试系统可执行的测试激励形式进行配置,且如果配置数据较多,这个转换过程将可能比较复杂,易用性不强,无法高效地用于FPGA器件的测试中,需要对FPGA测试设计专用的测试平台以满足其配置测试需求。

我们设计的系统实现了快速重复配置和测试的功能,配置数据可以直接引用EDA软件生成的位流文件而不需要像ATE一样转换成繁杂的测试激励形式,相较于ATE有一定的优势,对FPGA测试有一定的使用价值。

FPGA可重复配置和测试系统结构概述

系统框图如图1所示。

图1 可重复配置测试系统结构框图

系统功能的实现包括软件和硬件两部分。硬件部分包含PCI桥接芯片、FPGA1中的数据接口模块、配置模块、测试模块和被测FPGA。软件部分包含对实现FPGA配置部分的代码和实现FPGA测试部分的代码。FPGA1中的各硬件模块通过EDA软件以JTAG接口固化FPGA1中,其中FPGA1中的配置模块负责接收来自PC方软件发送的配置数据,并产生对被测FPGA的配置时序,完成配置步骤,测试模块负责发送测试激励和回收被测FPGA的响应数据,等待PC方软件的回收。

系统软硬件交互流程

整个系统通过软硬件的数据交互实现对被测FPGA的自动配置和测试的流程,软硬件交互的流程从图2可以体现:系统启动后,首先需要开始对被测FPGA进行数据配置,由软件向硬件发送配置开始指令,硬件接收指令后对被测FPGA产生配置开始的时序,告诉被测FPGA准备接收配置数据。当软件查询到配置模块中的状态寄存器值代表等待数据时开始发送配置数据。配置数据发送完成后,软件通过读取配置模块的状态寄存器值判断配置是否成功,决定是否可以开始测试。如果配置成功,软件则开始向被测FPGA发送测试激励数据并读回测试响应保存在电脑中,由软件对测试响应进行分析决定是否需要进行下一次配置和测试流程。如果需要,在一定的延时之后软硬件将回复初始状态,并选择新的配置数据和测试数据,开始新一轮的配置后测试流程。

图2 FPGA芯片自动重复下载自动测试系统软硬件交互流程图

软硬件数据交互的通路是PCI总线,软件向FPGA1发送指令或数据时,软件通过PCI应用编程接口函数将数据放到PCI总线上,PCI桥接芯片将较为复杂的PCI接口信号转化为相对简单的Local Bus数据信号,由FPGA1中的接口模块接收并产生相应的动作。而软件向FPGA1读取数据的通路则相反。图3和图4分别是软件在VC++6.0环境中断点调试发送指令和软件向FPGA1发送指令时由嵌入式逻辑分析仪SignalTAP II捕捉到的指令数据和接口模块波形。

图3 VC++6.0环境中断点调试指令发送

图4 嵌入式逻辑分析仪SignalTAP II波形

图4中ADS_N、BLAST_N、LWORD_N、LHOLD、LHOLDA是Local Bus的接口信号,ConfigEnd和ConfigStart是分别代表配置结束和配置开始的标志寄存器,LA是接口的地址信号,用于模块中控制寄存器的寻址,LD是接口的数据信号,用于指令数据的发送和数据的回收。

以配置开始指令的发送为例,从图3图4两图中可以看出软硬件交互过程中的指令发送方式,在VC++中单步调试,发送一个开始指令0x01到配置命令寄存器地址0x01,通过硬件模块的接口动作,用嵌入式存储器SignalTap II中捕捉到LA的数据为1h,LD上的数据为1h后ConfigStart寄存器置高,配置开始。

配置速度测试实验

软硬件具体方案设计完毕后,软件在Visual C++6.0环境下实现并调试。硬件在QuartusII7.1软件下编译。

为了对比基于PCI总线的FPGA高速配置方案与基于ByteBlasterII JTAG下载电缆的速度性能,首先使用QuartusII7.1软件采用JTAG方式对FPGA2配置5次,计算每次下载所示时间,得到如表1中所示的数据;再使用本系统中基于PCI总线的配置功能对FPGA2配置5次,软件会自行计算总的下载时间,得到如表1中所示的数据:

从表1的数据对比中可以看到,基于PCI总线的自动下载配置方式要比基于JTAG电缆的下载配置方式提高超过20倍的速度,如果使用基于JTAG电缆对某大容量的FPGA下载需要近20分钟的话,使用PCI下载方式则只需不到1分钟的下载时间,具有明显的速度优势,大大节省了FPGA测试中的数据配置时间。

FPGA 集成电路 电路 EDA 总线 嵌入式 Quartus 自动化 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)