VHDL设计MOORE型有限状态机时速度问题的探讨

2.3 输出直接从状态位得到

为了能够把时钟-输出时延限制在TCO内,也可以将状态位本身作为输出信号。对于状态位不是很多的状态机而言,这种方法也许较前两种更为优越。某种情况下,可能会出现两种不同状态有相同的状态位,此时只需增加一位状态位加以区别即可。如此程序中,idle、decision、read、write四种状态可分别编码为000,001,100,010。采用这种方法所对应的程序如下:

signalpresent_state:std_logic_vector(2downto0);

state:process(clk,ready,read_write);

begin

if(clk'eventandclk='1')then

case present_stateis

when "000"=>ifready='1' then present_state<="001";

else present_state<="000";

endif;

when "001"=>if(read_write='1') then

present_state<="100";

else present_state<="001";

endif;

when "100"=>if(ready='1')then

present_state<="000";

elsepresent_state<="100";

endif;

when "010"=>if(ready='1') then present_state<="000";

else present_state<="010";

endif;

when others=>present_state<="---";

endcase;

endif;

endprocess;

oe<=present_state(2);

wr<=present_state(1);

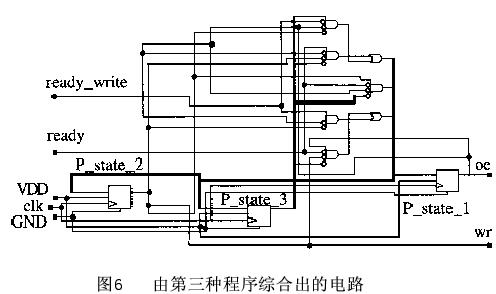

对此程序综合出的电路如图6所示。从图中可知,输出信号未通过额外的逻辑对现态进行译码,而是直接来自状态寄存器,因而输出信号上没有毛刺,并且它所用的宏单元少于通过并行输出寄存器输出的方式。

3 结论

从以上分析可知,普通MOORE型状态机时延最长,速度最慢,可应用于对速度要求不高的场合。同时,由于它的输出信号中有毛刺,更加限制了它的应用范围。后两种方案在相同的条件下,具有相同的时延,即速度是相同的,但第二 种方案所占用面积要比第三种大得多,且对时钟频率有一定限制。如果可能的话,选择“输出直接从状态位得到”类型状态机是一个理想的方案,因为其速度最快,面积最小,设计这种状态机时,必须在VHDL源码中对状态的编码加以明确的规定,使状态和输出信号的取值一致。所以只有在状态机的规模较小时,才能很好地实现这种类型的设计。

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)