如何实现微控制器与FPGA的接口设计

3 在MCU中使用专用的FPGA接口 图7 MCU专用的FPGA接口 图8 ARM7与FPGA接口 图9 串行单配置 图10 双串行配置 表1 模式位

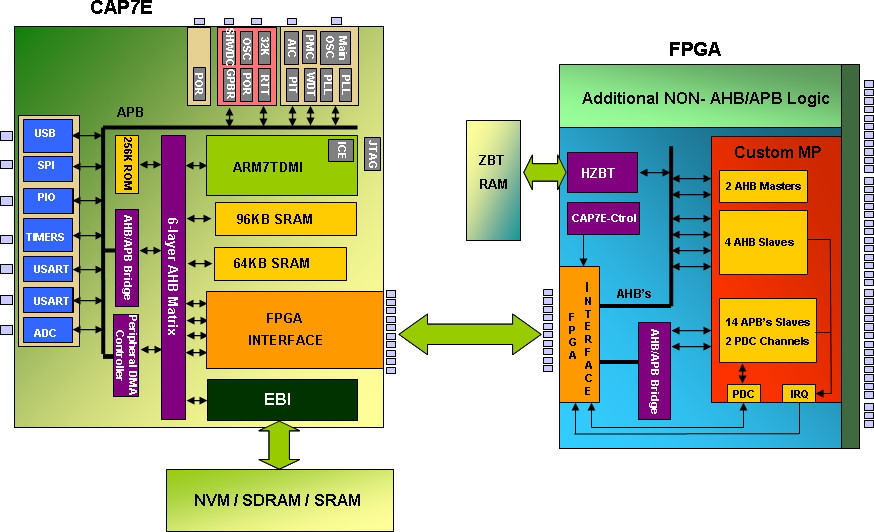

基于ARM7的微控制器提供一个特殊接口,它允许FPGA通过DMA存取2个主AHB和四个副AHB直接接入MCU的内部AHB总线。在启动时,一个外加的副AHB可用于重新映射ROM,它通过使用外部ZBT RAM具有PROM重新映射功能的FPGA来实现。

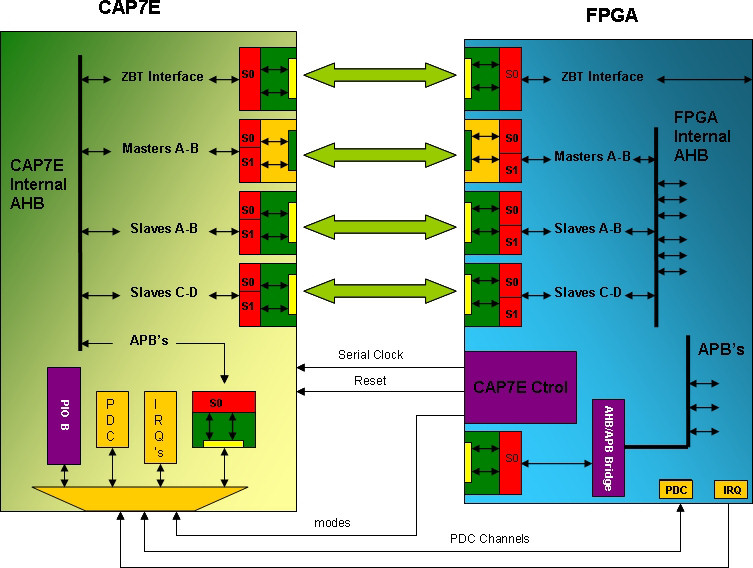

该接口还提供了FPGA接入14个副先进外围总线(APB)、两个全双工的DMA通道、多达13个中断优先编码(IRQs)、两个DMA传输的非编码IRQs和32位共享可编程I/O。该FPGA接口通过微控制器接入预先定义的主副AHB(图7)。

FPGA接口是基于多个并串行转换器来编码和解码所有微控制器和FPGA之间的业务流。为了使两个不同设备之间能进行有效的同步通信,必须满足以下要求:

在FPGA必须能够处理时钟偏斜平衡和时延消除。赛灵思的FPGA采用DCM(数字时钟管理器)强制性处理所有时延消除,且要求产生时钟。Altera的器件需要使用锁相环电路。该FPGA还必须为微控制器的内置接口提供配置和复位方式。它必须为微控制器提供的串行通信时钟,频率范围应在100兆赫以上。ARM7的内部时钟和串行时钟之间的比率应为0.8或更低(ARM的时钟/串行时钟)。

FPGA接口是基于一套编码和解码AHB内部业务流的单元。各主从AHB编码/解码的数据传输通过使用专用并串行转换器的MPIO来实行。由于传送大量数据,一个单一的传输就消耗多个AHB总线时钟周期。具体所需的时钟周期取决于ARM7中的AHB时钟、串行时钟和FPGA中的AHB时钟之间的比例。由于微控制器的AHB时钟与FPGA中的AHB时钟之间相互独立, FPGA和微控制器可以在不同的频率运行。甚是FPGA内的主或副AHB时钟可以在不同的频率运行。

微控制器和FPGA上的每个并串行转换器阻滞都有一个互补的有限状态机(FSM)与AHB总线打交道。因此,该接口可以借鉴EBI或PIO消除共同接口瓶颈的技术来处理同步传输问题。

带有直接FPGA接口的微控制器几乎所有的外围都有DMA通道,有几个DMA通道专用于FPGA的接口。多通道外围DMA控制器( PDC )支持该DMAs,像其他两种方法一样,在FPGA、外设和存储器之间传输数据时通过CPU卸荷。这避免了普通ARM7的带宽限制,它被只有4万比特每秒(Mbps)数据传输速率完全垄断。

通过从CPU中卸下这一任务, PDC可以实现处理时间占85 %CPU周期,数据传输率12 Mbps。多重DMA通道是专为FPGA接口连接PDC多个特定应用的外设和接口而设的,不受微控制器的任何干预。在PDC中使用DMA专用通道,可以使ARM处理器有时间把重点放在处理器的繁重任务上,提高系统的总体性能和数据带宽(图8)。

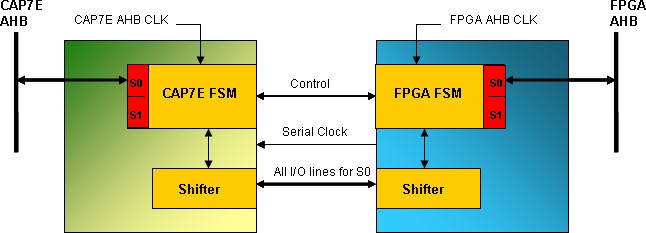

该并串行转换器模块能处理所有的AHB和串行通讯。它由一个有限状态机(FSM)和移位器组成。有限状态机解读AHB,并与AHB对话。当主AHB初始化一个传输(读/写操作)时,FSM通过使用遵守的AHB协议的HREADY来引入等待状态。FSM直接根据AHB时钟和串行时钟之间的比例来自动处理引入等待周期的数量。比例越小,引入的等待周期就越少。

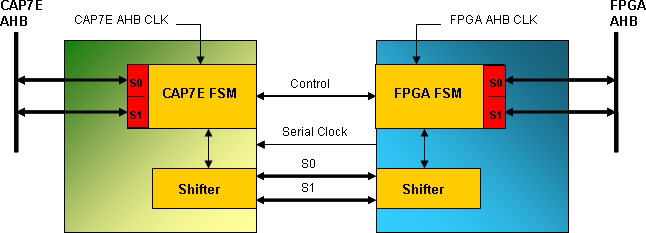

FSM控制移位器,负责处理所有微控制器和FPGA之间的数据转移(序列化),每周期传输在2个bits的数据。如果串行时钟速率为100兆赫,移位器的传输速度为200 Mbps。

这些并串行转换器模块处理主口A / B、副口A / B和副口C/D,通过FPGA 内的“模式”模块在复位时程序化,使可用的I / O数量尽可能多。设计者可以为一个单一的串行配置选择使用所有的10个I / O线。在这种情况下,串行模块将只处理一个的AHB接口。例如,如果用户仅想使用AHB主口A,串行模块将所有主口设定为“串行单配置” 。这种配置将改善转换器之间的传输速度,从而加快了微控制器和FPGA之间的传输速度(图9)。

另一种选择是配置串行模块为“双串行配置”使其能处理2个AHB接口,2个AHB (主/副)之间共用10个I / O线。在这种情况下,微控制器和FPGA之间的数据传输速率较低,但数据带宽更高,因为有2个AHB接口可用。双配置给另一个AHB接口重新使用一半以上的专用I / O(图10)。

4 FPGA的接口逻辑

当通过EBI或PIOs执行一个FPGA接口时,工程师必须写RTL代码,让FPGA与MCU进行沟通。直接FPGA接口微控制器供应商提供的所有RTL需要为每个具体的FPGA供应商建立适当的编码和解码通信限制。这种逻辑模块产生一个重置,并提供不同模式下的重置条件。供应商提供的RTL可让用户来决定选择哪些功能来。默认情况下,所有的模式位0 (表1)。

一个供应商提供的模板可用于FPGA接口的主从AHB实例。提供具体的例子。在FPGA模板,一个模块所谓的“自定义MP”不费力的整合AHB / APB外设。因为系统将使用FPGA逻辑,此模板让设计师使用迁移的两片MCU加FPGA毫不费力的实现单芯片可定制微控制器。

外部ZBT-RAM和NVM/SDRAM/SRAM是可选的,它基于应用程序和系统要求。

设计人员还可以在FPGA添加非AHB逻辑,为添加与AHB总线无关的功能提供了灵活性。

在单一配置模式下,单一AHB接口从微控制器传输所有的AHB信息到FPGA需要4个AHB时钟周期,反之亦然(图11 ) 。在双配置模式下,双AHB接口从微控制器传输所有的AHB信息到FPGA需要8个AHB时钟周期,反之亦然。

嵌入式 FPGA 单片机 MCU ARM 电路 总线 赛灵思 Altera 显示器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)