FPGA协处理器的优势

时间:09-26

来源:互联网

点击:

- Xilinx ESL计划

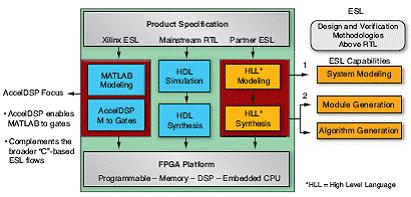

ESL设计工具将数字设计的抽象度在RTL的基础上又提高了一步。其中部分工具专门用来将由C/C++开发的系统模型映射到包含FPGA和DSP处理器的DSP系统中。此举的目的是使硬件平台对软件设计者变得透明(图4)。

图4 – Xilinx ESL计划的设计流程。

今年,为了全面解决上述障碍,Xilinx公司和主要的ESL工具厂商携手启动了一个被称为ESL计划的合作项目。这一合作计划的主要目标是赋予设计者软件编程的能力,使他们能够在可编程硬件中轻松地实现自己的想法,而无需学习传统的硬件设计技巧。该计划融合了ESL成员机构的创新,能够加速产品开发进程,推动设计人员采用世界上最先进的设计方法。

结论

将Xilinx ESL合作伙伴的工具结合在一起,能够提供广泛的互补性解决方案,这些解决方案已针对一系列产品、平台和最终用户进行了优化。Xilinx公司也在集中力量研究互补技术。例如,AccelDSP综合为在浮点MATLAB中开发的算法提供了硬件实现的方法,而Xilinx System Generator for DSP使得用ESL设计开发的模块,能够轻松地与Xilinx IP和嵌入式处理器结合起来。借助多个极富创新精神的合作伙伴的工作,是实现程序员期望的FPGA设计流程最快捷的途径。

- Xilinx ESL计划

DSP C语言 FPGA VHDL Xilinx 嵌入式 总线 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- FPGA作为协处理器在实时系统中的应用(04-08)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)

- 基于Spartan-3A DSP的安全视频分析(05-01)