原型验证过程中的ASIC到FPGA的代码转换

时间:09-21

来源:互联网

点击:

代码转换的实现

结合同济大学微电子中心的“32位高性能嵌入式cpu开发”项目,为了在流片之前确保功能的可靠性,对32位全定制高性能嵌入式cpu bc320进行了原型验证。

设计采用memec design公司的ff1152开发板。该板使用了xilinx的virtex-ⅱ pro系列芯片中的xc2vp30。该fpga拥有30 816个逻辑单元,相当于有30多万的asci门。另有2mb的片上block ram,644个i/o口。采用了xilinx的全自动、完整的集成设计环境ise 7.1i,进行fpga综合使用的工具是synplify pro。

用bc320的ASIC rtl代码作为fpga的输入,具体的代码转换如下。

存储单元

设计中用到了很多sram,例如icache中的sram。在fpga实现时根据所需ram的宽度、深度和功能来决定采用哪种单元来进行替换。xilinx提供了片外ram、block ram和lut ram。

ise提供了两种具体的实现方法:ip生成器(core generator)和语言模板(language templates)。ip生成器是xilinx fpga设计中的一个重要设计输入工具,它提供了大量xilinx和第三方公司设计的成熟高效ip核。

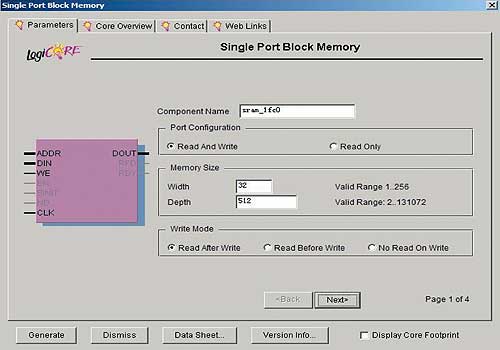

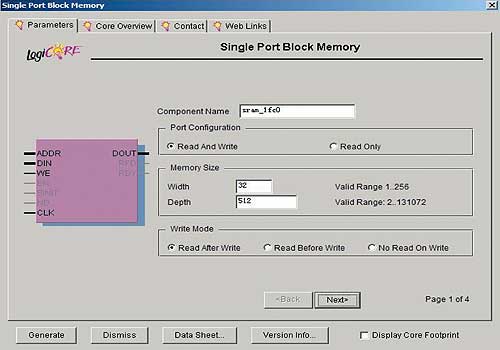

这里是用core generator来产生了名为块存储器(block memory)的单口存储器模块。core generator用图形化设置参数的方式来提供块存储器,其界面如图5所示。块存储器的大小根据向量的大小来制定,一个普通单元向量只需要4个512×32bit的块存储器就够了。core generator产生块存储器时,除了参数设置外,还需要输入一个为.coe的文件来初始化块存储器的内容。core generator产生的文件同时考虑了后端执行和仿真两方面,主要有三个文件:file.v,file.mif,file.edn。其中.v文件为verilog格式的sram仿真模型; .mif文件为作为其初始化内容,其内容和.coe文件里的具体向量内容是一致的;而实际后端文件为.edn,包含了块存储器的全部信息。

图5 ip生成器的界面

language templates主要利用xilinx的块存储器元件库,直接进行调用。xc2vp30内部的单口块存储器型号主要有:16k×1bit、1k×16bit、2k×8bit、4k×4bit、512×32bit、8k×2bit。可以根据自己的需要随意调用这些模块,在rtl代码中实例化,并把sram初始值作为参数传递进去。这些模块在synplify pro中根据选定的fpga型号被自动识别,然后综合成统一的.edn文件,再进行后续操作。语言模板方式的灵活性比较强,可以设置多个不同位宽,不同深度的块存储器,仿真也比较方便,但是参数设定时,sram初始值的设置比较麻烦。

另外,xilinx提供工具data-mem,它可以每次只改变fpga中块存储器的内容,而不需将整个设计重新翻译、映射和布局布线,为大量的向量验证节约了时间。

时钟单元

在bc320设计中,cpu内核通过sysad接口与外部sram连接。这些外部sram的时钟和主时钟是不一致的,在asic中,用一个pll来实现。这个pll模块是无法用synplify pro综合的,在fpga上必须将它用xilinx的数字时钟管理模块(dcm)来替换。同样可以利用core generator和language templates这两种方法。

利用core generator产生mydcm.v文件来代替原先的pllgs_500.v,代码如下。第二段代码是修改后的代码。

module pllgs_500( pll_k,

pll_m,

pll_n,

pll_pd,

pll_tst,

reset,

xin,

clk_out,

tst_out);

module mydcm(clkin_in,

rst_in,

clkfx_out,

clkin_ibufg_out,

locked_out);

时钟使能带代替门控时钟

把实现门控时钟信号转换成实现使能信号,例如信号pcepl,代码如下。第二段代码是修改后的代码。

module(out,in,clk, pcepl);

……

always @ (clk or pcepl)

assign pceplv= pcepl & clk;

always @(posedge pceplv)

begin

out <= in;

end

endmodule

module(out,in,clk, pcepl);

……

always @(posedge clk)

begin

if (pcepl)

out <= in;

else

out <= out;

end

endmodule

外部器件配置单元和顶层封装

在ff1152开发板上集成了很多接口和器件,在原型验证时,可以充分利用这些接口和器件做为和设计的交互环境。这些接口和器件需要正确配置后才能正常工作,这部分配置工作可以用FPGA实现。

设计增加了lcd接口单元、内部记分牌(scoreboard)模块和通用异步串行接收发送(uart)模块。作为保存向量内容的sram设定好后,可以用同样的方法将寄存器参考值也保存在另外的块存储器中。然后运行cpu,将cpu实际产生的寄存器值和已保存过的参考值在记分牌模块中进行实时比较,然后将结果输出到lcd显示屏上。

为了便于代码的管理和维护,可以对原rtl代码进行一定的封装。将原ASIC流程的代码单独封装在一个模块中,再和fpga实现时添加的片外配置控制单元的代码一起形成新的fpga实现顶层。

所以在asic代码的基础上增加了对这几个器件完成配置工作的代码部分。

为了原型系统获得更高的性能,还可以对其他一些模块的代码进行适当的改进,如算术单元和状态机的编码风格等。但对于全定制的cpu bc320,没有必要修改算术单元模块的代码,关键是存储模块和时钟单元。因此要根据自己的设计适当选择要修改的代码。

结合同济大学微电子中心的“32位高性能嵌入式cpu开发”项目,为了在流片之前确保功能的可靠性,对32位全定制高性能嵌入式cpu bc320进行了原型验证。

设计采用memec design公司的ff1152开发板。该板使用了xilinx的virtex-ⅱ pro系列芯片中的xc2vp30。该fpga拥有30 816个逻辑单元,相当于有30多万的asci门。另有2mb的片上block ram,644个i/o口。采用了xilinx的全自动、完整的集成设计环境ise 7.1i,进行fpga综合使用的工具是synplify pro。

用bc320的ASIC rtl代码作为fpga的输入,具体的代码转换如下。

存储单元

设计中用到了很多sram,例如icache中的sram。在fpga实现时根据所需ram的宽度、深度和功能来决定采用哪种单元来进行替换。xilinx提供了片外ram、block ram和lut ram。

ise提供了两种具体的实现方法:ip生成器(core generator)和语言模板(language templates)。ip生成器是xilinx fpga设计中的一个重要设计输入工具,它提供了大量xilinx和第三方公司设计的成熟高效ip核。

这里是用core generator来产生了名为块存储器(block memory)的单口存储器模块。core generator用图形化设置参数的方式来提供块存储器,其界面如图5所示。块存储器的大小根据向量的大小来制定,一个普通单元向量只需要4个512×32bit的块存储器就够了。core generator产生块存储器时,除了参数设置外,还需要输入一个为.coe的文件来初始化块存储器的内容。core generator产生的文件同时考虑了后端执行和仿真两方面,主要有三个文件:file.v,file.mif,file.edn。其中.v文件为verilog格式的sram仿真模型; .mif文件为作为其初始化内容,其内容和.coe文件里的具体向量内容是一致的;而实际后端文件为.edn,包含了块存储器的全部信息。

图5 ip生成器的界面

language templates主要利用xilinx的块存储器元件库,直接进行调用。xc2vp30内部的单口块存储器型号主要有:16k×1bit、1k×16bit、2k×8bit、4k×4bit、512×32bit、8k×2bit。可以根据自己的需要随意调用这些模块,在rtl代码中实例化,并把sram初始值作为参数传递进去。这些模块在synplify pro中根据选定的fpga型号被自动识别,然后综合成统一的.edn文件,再进行后续操作。语言模板方式的灵活性比较强,可以设置多个不同位宽,不同深度的块存储器,仿真也比较方便,但是参数设定时,sram初始值的设置比较麻烦。

另外,xilinx提供工具data-mem,它可以每次只改变fpga中块存储器的内容,而不需将整个设计重新翻译、映射和布局布线,为大量的向量验证节约了时间。

时钟单元

在bc320设计中,cpu内核通过sysad接口与外部sram连接。这些外部sram的时钟和主时钟是不一致的,在asic中,用一个pll来实现。这个pll模块是无法用synplify pro综合的,在fpga上必须将它用xilinx的数字时钟管理模块(dcm)来替换。同样可以利用core generator和language templates这两种方法。

利用core generator产生mydcm.v文件来代替原先的pllgs_500.v,代码如下。第二段代码是修改后的代码。

module pllgs_500( pll_k,

pll_m,

pll_n,

pll_pd,

pll_tst,

reset,

xin,

clk_out,

tst_out);

module mydcm(clkin_in,

rst_in,

clkfx_out,

clkin_ibufg_out,

locked_out);

时钟使能带代替门控时钟

把实现门控时钟信号转换成实现使能信号,例如信号pcepl,代码如下。第二段代码是修改后的代码。

module(out,in,clk, pcepl);

……

always @ (clk or pcepl)

assign pceplv= pcepl & clk;

always @(posedge pceplv)

begin

out <= in;

end

endmodule

module(out,in,clk, pcepl);

……

always @(posedge clk)

begin

if (pcepl)

out <= in;

else

out <= out;

end

endmodule

外部器件配置单元和顶层封装

在ff1152开发板上集成了很多接口和器件,在原型验证时,可以充分利用这些接口和器件做为和设计的交互环境。这些接口和器件需要正确配置后才能正常工作,这部分配置工作可以用FPGA实现。

设计增加了lcd接口单元、内部记分牌(scoreboard)模块和通用异步串行接收发送(uart)模块。作为保存向量内容的sram设定好后,可以用同样的方法将寄存器参考值也保存在另外的块存储器中。然后运行cpu,将cpu实际产生的寄存器值和已保存过的参考值在记分牌模块中进行实时比较,然后将结果输出到lcd显示屏上。

为了便于代码的管理和维护,可以对原rtl代码进行一定的封装。将原ASIC流程的代码单独封装在一个模块中,再和fpga实现时添加的片外配置控制单元的代码一起形成新的fpga实现顶层。

所以在asic代码的基础上增加了对这几个器件完成配置工作的代码部分。

为了原型系统获得更高的性能,还可以对其他一些模块的代码进行适当的改进,如算术单元和状态机的编码风格等。但对于全定制的cpu bc320,没有必要修改算术单元模块的代码,关键是存储模块和时钟单元。因此要根据自己的设计适当选择要修改的代码。

FPGA 集成电路 仿真 电路 总线 电子 嵌入式 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)