基于FPGA和SRAM的数控振荡器的设计与实现

时间:09-17

来源:互联网

点击:

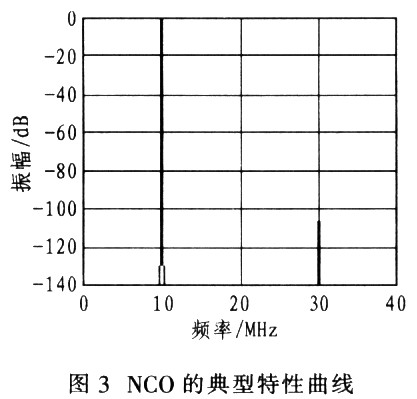

3.3 NCO性能评估

按照上述结构.笔者设计了一种NCO系统。该系统的工作时钟为80MHz.用DSP作为微处理器。通过系统测试.该NCO的性能指标达到了设计要求,频率分辨率△f=O.0186Hz,信噪比(SNR)在100dB以上.图3示出NCO的典型特性曲线。

4 结构特点

用FPGA和SRAM实现数控振荡器有许多特点。

首先,查找表的容量可以进一步加大。此设计的结构把相位累加部分和查找表分开单独实现.由于FPGA具有可重复编程性且有丰富的I/O资源,因此只要稍加改动FPGA内的逻辑设计就可以外挂更大容量的SRAM。

其次,载波样本的数据位数可以灵活控制。在查找表容量一定的情况下,可以根据具体应用调整载波样本的数据宽度。实现的手段有二:一是在对SRAM配置时通过微处理器以软件编程的方式直接调整SRAM的数据宽度:二是在FPGA内对SRAM输出数据的位数进行截位处理.可通过调整FPGA中锁存器的输出实现。

第三,能够灵活应用到其他领域中。该NCO只消耗FPGA中6%的Slices资源,大量资源包括片内RAM和硬件乘法器都没有用到,利用这些资源可以对NCO进行功能扩展,实现数字下变频器(Digital Down Converter-DDC)、数字频率合成器(Direct Digital Synthesizer-DDS)和调制解调器等。

5 结束语

本文介绍了一种新的NCO实现方法,用该方法设计的NCO可实现对载波的频率、相位和幅度的完全控制。由于用独立的大容量SRAM作为查找表,使得NCO有较高的精度。同时该NCO有很大的发挥空间,能够灵活地运用到其他领域。

振荡器 信号发生器 FPGA Xilinx Cypress 单片机 VHDL DSP 相关文章:

- 数字下变频的FPGA实现(05-12)

- 基于FPGA的任意时延伪码序列产生方法(04-12)

- 在嵌入式设计中降低CPLD的功耗(04-30)

- Actel数模结合FPGA的远程控制器设计(05-13)

- 基于FPGA的相检宽带测频系统的设计(06-08)

- ACEX 1K系列CPLD配置方法探讨(06-09)