基于并行流水线结构的可重配FIR滤波器的FPGA实现

时间:09-16

来源:互联网

点击:

3 仿真及测试

用VHDL语言描述全部电路模块后,输入系数1、2、3、4、5和数据-l、-2、3、4等进行测试.用Mod-elsim进行仿真,其结果如图3所示。

可以看出,模块能正确进行计算,从数据输入到数据输出约延时2个数据时钟.这主要是前面的数据输入模块的延时。乘加部分采用数据时钟的N/2倍,其延时与滤波器的阶数成比例,但不会超过一个数据时钟周期。

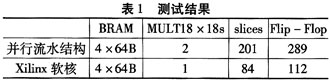

然后,对VHDL描述就Xilinx的Spartan-3进行综合和测试。可以得出表1所示的测试结果,其中第一行为并行流水结构所设计的滤波器,第二行是采用Xilinx提供的软核设计的滤波器。

可以看出,除了增加一个乘法器外,逻辑块和触发器都增加了一倍多。用这种结构设计的滤波器面积增加了一倍,速度性能也提高了一倍。以上两种滤波器可以应用在语音信号处理中--让语音信号通过低通滤波器以获取语音的低频分量。相对而言,并行流水结构能实现比Xilinx软核更高阶数的滤波器。在听觉上,经过两种滤波器(相同阶数)的语音信号没有太大差别。

4 结束语

本文在运算层次上,依据流水和并行运算结构实现直接型FIR滤波器。如果在设计滤波器时,结合级联型和直接型两种滤波器结构,那么也能实现同样的并行和流水的效果。实际上,还可在更低层次的乘法运算时,对部分和也用并行和流水结构来实现。这些结构的选择都依据性能要求和实现的复杂性来具体确定。

作为实现现代高性能处理器的方法,并行和流水结构各有特点。并行是以面积换速度。流水是以延时换速度,采用这两种结构,就能在面积、速度、延时之间灵活互换。

用VHDL语言描述全部电路模块后,输入系数1、2、3、4、5和数据-l、-2、3、4等进行测试.用Mod-elsim进行仿真,其结果如图3所示。

可以看出,模块能正确进行计算,从数据输入到数据输出约延时2个数据时钟.这主要是前面的数据输入模块的延时。乘加部分采用数据时钟的N/2倍,其延时与滤波器的阶数成比例,但不会超过一个数据时钟周期。

然后,对VHDL描述就Xilinx的Spartan-3进行综合和测试。可以得出表1所示的测试结果,其中第一行为并行流水结构所设计的滤波器,第二行是采用Xilinx提供的软核设计的滤波器。

可以看出,除了增加一个乘法器外,逻辑块和触发器都增加了一倍多。用这种结构设计的滤波器面积增加了一倍,速度性能也提高了一倍。以上两种滤波器可以应用在语音信号处理中--让语音信号通过低通滤波器以获取语音的低频分量。相对而言,并行流水结构能实现比Xilinx软核更高阶数的滤波器。在听觉上,经过两种滤波器(相同阶数)的语音信号没有太大差别。

4 结束语

本文在运算层次上,依据流水和并行运算结构实现直接型FIR滤波器。如果在设计滤波器时,结合级联型和直接型两种滤波器结构,那么也能实现同样的并行和流水的效果。实际上,还可在更低层次的乘法运算时,对部分和也用并行和流水结构来实现。这些结构的选择都依据性能要求和实现的复杂性来具体确定。

作为实现现代高性能处理器的方法,并行和流水结构各有特点。并行是以面积换速度。流水是以延时换速度,采用这两种结构,就能在面积、速度、延时之间灵活互换。

FPGA 集成电路 滤波器 VHDL Xilinx 仿真 电路 低通滤波器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)