基于CPLD的数字滤波抗干扰电路设计

时间:09-17

来源:互联网

点击:

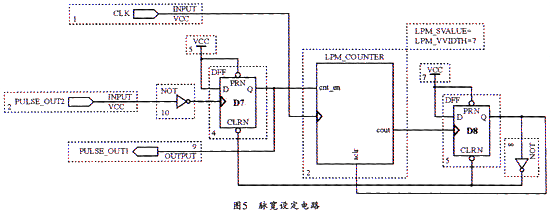

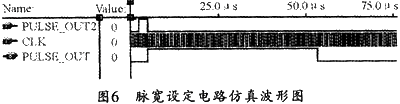

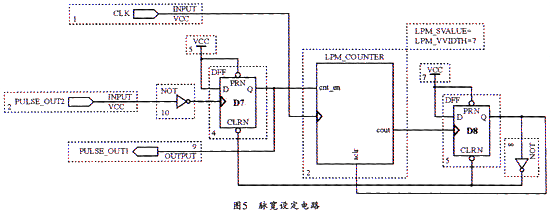

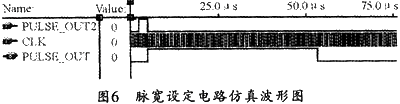

2.4 脉宽设定电路

为了保证弹丸穿过光幕所产生的脉冲信号能够适合后续处理电路的需要,本设计将弹丸穿过光幕产生的脉冲信号全部变为脉宽为50μs的脉冲信号再输出给后续电路。图5和图6分别是其脉宽设定电路及其仿真波形图。图中,当PULSE_OUT2有一个正跳变时,触发器D7的输出端输出高电平并启动计数器。当计数器计满时,计数器cout出现上升沿,触发器D8的输出端输出高电平,此高电平信号将计数器清零,同时经反相器反相后接到触发器D7和D8清零端,以将触发器D7和D8清零。

在这种情况下,对于整个系统电路来说,当PULSE_IN上跳沿到来并经过抗冲击波电路后,若信号脉宽小于10μs,则输出PULSE_OUT为低电平;作用就是若信号脉宽大于10μs,则启动抗蚊虫干扰电路;若信号脉宽大于150μs,输出PULSE OUT则为低电平;而若脉宽小于150μs,则经过脉宽设定电路变成宽度为50μs的信号输出,从而使PULSE_OUT输出宽度为50μs的脉冲信号。

通过上述分析可知,应用CPLD可编程逻辑器件所设计的抗干扰电路具有信号可灵活调节、脉宽修改方便、对输入信号的脉宽适应能力强、可调节范围大、输出的脉冲宽度和幅值稳定准确等特点。

3 结束语

在测试弹丸射击密集度时,可利用CPLD器件设计抗干扰电路来消除冲击波和蚊虫干扰信号。本文给出的电路设计简单可靠,能有效地消除干扰脉冲,从而保证数据的准确性和可靠性。经重庆某靶场实际应用证明,本电路具有良好的效果。

为了保证弹丸穿过光幕所产生的脉冲信号能够适合后续处理电路的需要,本设计将弹丸穿过光幕产生的脉冲信号全部变为脉宽为50μs的脉冲信号再输出给后续电路。图5和图6分别是其脉宽设定电路及其仿真波形图。图中,当PULSE_OUT2有一个正跳变时,触发器D7的输出端输出高电平并启动计数器。当计数器计满时,计数器cout出现上升沿,触发器D8的输出端输出高电平,此高电平信号将计数器清零,同时经反相器反相后接到触发器D7和D8清零端,以将触发器D7和D8清零。

在这种情况下,对于整个系统电路来说,当PULSE_IN上跳沿到来并经过抗冲击波电路后,若信号脉宽小于10μs,则输出PULSE_OUT为低电平;作用就是若信号脉宽大于10μs,则启动抗蚊虫干扰电路;若信号脉宽大于150μs,输出PULSE OUT则为低电平;而若脉宽小于150μs,则经过脉宽设定电路变成宽度为50μs的信号输出,从而使PULSE_OUT输出宽度为50μs的脉冲信号。

通过上述分析可知,应用CPLD可编程逻辑器件所设计的抗干扰电路具有信号可灵活调节、脉宽修改方便、对输入信号的脉宽适应能力强、可调节范围大、输出的脉冲宽度和幅值稳定准确等特点。

3 结束语

在测试弹丸射击密集度时,可利用CPLD器件设计抗干扰电路来消除冲击波和蚊虫干扰信号。本文给出的电路设计简单可靠,能有效地消除干扰脉冲,从而保证数据的准确性和可靠性。经重庆某靶场实际应用证明,本电路具有良好的效果。

红外 传感器 电压 比较器 电路 CPLD 仿真 相关文章:

- 基于FPGA的远程图像采集系统设计(11-23)

- Actel数模结合FPGA的远程控制器设计(05-13)

- 基于FPGA的二值图像连通域标记快速算法实现(07-24)

- 关于CPLD和接触式图像传感器的图像采集系统(07-26)

- FPGA的光电抗干扰电路设计(08-07)

- StrongARM及其嵌入式应用平台(08-30)