一种基于CPLD的数据采集控制板的设计

时间:09-18

来源:互联网

点击:

在需要采集多路模拟信号、开关信号、频率(计数)信号以及编码器信号等的数据采集应用中,利用通用板卡构成计算机测控系统是可行的,但对于产品的批量应用,其成本与综合性能不能令人满意。技术成熟的CPLD芯片的应用,可以很好地将逻辑控制、数据信号处理等功能集于一身,使以往需要利用多块信号板卡才能完成的任务整合于同一采集控制器中,从而有效地提高控制系统的可靠性,降低测控系统的实现成本。

本文设计一种基于CPLD的数据采集控制板。它能实现信号采集与控制、信号处理、通讯及输出控制等功能。

1 总体设计方案

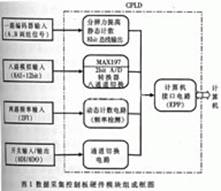

本专用数据采集控制板利用CPLD作为主控制器,统一协调通道切换与数字信号处理、实现数据采集与接口传输逻辑控制。该数据采集控制板共有四种类型的信号输入和一种开关信号量输出。图1给出其基本硬件模块组成。

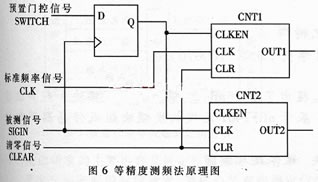

利用CPLD的资源和结构特点是本设计的核心。为提高编码器输入信号的分辨细长,配套设计一个四倍频电路,并在通道后端设计一个脉冲静态计数电路,使输入信号转换为8bit信号挂接到采集板总线上。八路模拟输入信号主要依靠CPLD实现通道切换和A/D采集,采样数据也以8bit信号并行进入总线。考虑到提高计数精度的要求,对两路频率输入信号设计了一个动态计数电路,使计数值通过总线读出。I/O切换控制、EPP接口电路等都按一定的逻辑要求采用同一CPLD元件来实现。如此可使硬件电路十分简单,并有利于上位机编程实现。

2 数据接口

根据IEEE1284标准,在标准并行口(SPP)、增强并行口(EPP)和扩展并行口(ECP)三种模式中,EPP模式既具有双向数据传输功能,又具有较高的数据传输能力,且编程操作相对容易,最适合在数据采集系统中使用。

从硬件设计角度考虑,EPP接口的主要功能之一是将采集到的数据上传给微型计算机或将开关控制命令下载到采集控制板(数据流对应8bit数据端口);之二是实现硬件接口之间的信号通讯握手(控制状态对应其它I/O端口)。EPP协议定义了四种数据传输基本操作:数据读、数据写、地址读、地址写。工作时首先写入I/O锁存地址即模块操作的I/O地址,然后进行相应的读出或写入操作。如果不需I/O地址变化,那么就不再进行I/O地址锁存操作。EPP模式下一共定义17根信号线,除8根双向地址线和数据复用线外,还有输出控制信号线WRITE、DSTROBE、ASTROBE、INIT,其中WRITE、DSTROBE和ASTROBE用于表示数据读写操作。WRITE为低时表示正在进行操作,DSTROBE为低表示进行数据操作,而ASTROBE为低则表示进行地址操作。EPP的INIT信号用来复位打印机,本设计用来预置光电编码器的初始计数值。另外还有五根状态信号线。WAIT信号由外设发出,高电平表示正在进行读写操作,低电平表示操作完成。但本设计没有利用该信号,因为前面三个读写信号已完全能满足要求。MAX197数据转换结束信号EOC连接到并口的SELECT线上,主机查询到SELECT线为低时,表示一次A/D转换结束,可以读取转换结果。其余三根状态线空置作为备用。

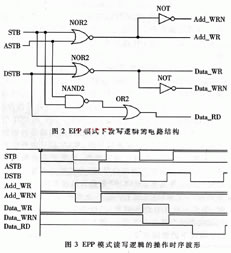

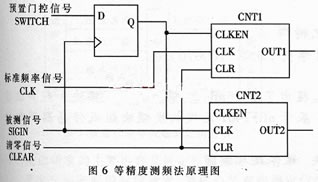

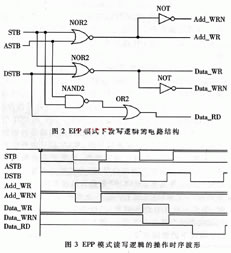

根据IEEE1284标准对EPP模式的地址、数据读写操作的规定,可采用图2的逻辑结构分别实现地址写、数据写和数据读。在图2中,输入信号中的STB表示写信号,ASTB表示地址写信号,DSTB表示数据写信号;输出信号中Add_WR表示地址写信号、高电平有效,Add_WRN表示地址写信号、低电平有效,Data_WR表示数据写信号、高电平有效、Data_WRN表示数据写信号、低电平有效;Data_RD表示数据读信号。如此设计的目的是使该接口能方便地适应各种逻辑器件的操作要求。图3给出了采用MAXPLUS软件对上述逻辑信号进行仿真的操作时序波形。

EPP模式可在上位机BIOS中设置或通过写ECR寄存器直接设置(并行适配器基地址为0X378H,I/O端口地址为77AH)。

3 编码器信号处理

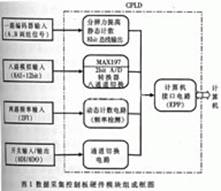

对于编码器输入信号,针对增量式光电编码器的输出具有A相、B相方波正交信号,而且二者相序取决于编码器的正反转方向,设计了一种四倍频及判向电路。

CLK信号来自独立振荡源,其频率高于编码器最大输出频率四倍以上,但也不宜过高,以免导致CPLD内部结构中信号竞争等问题。INA和INB分别为编码器输入的A相信号和B相信号,CNT_UP和CNT_DN分别为输出的正转倍频信号和反转倍频信号。为保证编码器处于任何转角位置都能可靠地读出数据,编码器倍频信号最终以16bit静态计数码方式输出,CNT_UP和CNT_DN分别作为后续静态计数电路的“加”和“减”计数输入信号端。在限定转动角度≤6×360°情况下,对于16bit计数码,计数电路允许的最大计数值为65536,计数值可以按高低八位分两次读出。为提高编码器工作可靠性,也可以考虑进行格雷码转换。

本文设计一种基于CPLD的数据采集控制板。它能实现信号采集与控制、信号处理、通讯及输出控制等功能。

1 总体设计方案

本专用数据采集控制板利用CPLD作为主控制器,统一协调通道切换与数字信号处理、实现数据采集与接口传输逻辑控制。该数据采集控制板共有四种类型的信号输入和一种开关信号量输出。图1给出其基本硬件模块组成。

利用CPLD的资源和结构特点是本设计的核心。为提高编码器输入信号的分辨细长,配套设计一个四倍频电路,并在通道后端设计一个脉冲静态计数电路,使输入信号转换为8bit信号挂接到采集板总线上。八路模拟输入信号主要依靠CPLD实现通道切换和A/D采集,采样数据也以8bit信号并行进入总线。考虑到提高计数精度的要求,对两路频率输入信号设计了一个动态计数电路,使计数值通过总线读出。I/O切换控制、EPP接口电路等都按一定的逻辑要求采用同一CPLD元件来实现。如此可使硬件电路十分简单,并有利于上位机编程实现。

2 数据接口

根据IEEE1284标准,在标准并行口(SPP)、增强并行口(EPP)和扩展并行口(ECP)三种模式中,EPP模式既具有双向数据传输功能,又具有较高的数据传输能力,且编程操作相对容易,最适合在数据采集系统中使用。

从硬件设计角度考虑,EPP接口的主要功能之一是将采集到的数据上传给微型计算机或将开关控制命令下载到采集控制板(数据流对应8bit数据端口);之二是实现硬件接口之间的信号通讯握手(控制状态对应其它I/O端口)。EPP协议定义了四种数据传输基本操作:数据读、数据写、地址读、地址写。工作时首先写入I/O锁存地址即模块操作的I/O地址,然后进行相应的读出或写入操作。如果不需I/O地址变化,那么就不再进行I/O地址锁存操作。EPP模式下一共定义17根信号线,除8根双向地址线和数据复用线外,还有输出控制信号线WRITE、DSTROBE、ASTROBE、INIT,其中WRITE、DSTROBE和ASTROBE用于表示数据读写操作。WRITE为低时表示正在进行操作,DSTROBE为低表示进行数据操作,而ASTROBE为低则表示进行地址操作。EPP的INIT信号用来复位打印机,本设计用来预置光电编码器的初始计数值。另外还有五根状态信号线。WAIT信号由外设发出,高电平表示正在进行读写操作,低电平表示操作完成。但本设计没有利用该信号,因为前面三个读写信号已完全能满足要求。MAX197数据转换结束信号EOC连接到并口的SELECT线上,主机查询到SELECT线为低时,表示一次A/D转换结束,可以读取转换结果。其余三根状态线空置作为备用。

根据IEEE1284标准对EPP模式的地址、数据读写操作的规定,可采用图2的逻辑结构分别实现地址写、数据写和数据读。在图2中,输入信号中的STB表示写信号,ASTB表示地址写信号,DSTB表示数据写信号;输出信号中Add_WR表示地址写信号、高电平有效,Add_WRN表示地址写信号、低电平有效,Data_WR表示数据写信号、高电平有效、Data_WRN表示数据写信号、低电平有效;Data_RD表示数据读信号。如此设计的目的是使该接口能方便地适应各种逻辑器件的操作要求。图3给出了采用MAXPLUS软件对上述逻辑信号进行仿真的操作时序波形。

EPP模式可在上位机BIOS中设置或通过写ECR寄存器直接设置(并行适配器基地址为0X378H,I/O端口地址为77AH)。

3 编码器信号处理

对于编码器输入信号,针对增量式光电编码器的输出具有A相、B相方波正交信号,而且二者相序取决于编码器的正反转方向,设计了一种四倍频及判向电路。

CLK信号来自独立振荡源,其频率高于编码器最大输出频率四倍以上,但也不宜过高,以免导致CPLD内部结构中信号竞争等问题。INA和INB分别为编码器输入的A相信号和B相信号,CNT_UP和CNT_DN分别为输出的正转倍频信号和反转倍频信号。为保证编码器处于任何转角位置都能可靠地读出数据,编码器倍频信号最终以16bit静态计数码方式输出,CNT_UP和CNT_DN分别作为后续静态计数电路的“加”和“减”计数输入信号端。在限定转动角度≤6×360°情况下,对于16bit计数码,计数电路允许的最大计数值为65536,计数值可以按高低八位分两次读出。为提高编码器工作可靠性,也可以考虑进行格雷码转换。

- 基于CPLD的开放式四轴运动控制器的设计(06-23)

- WCDMA速率适配算法的FPGA实现(07-11)

- 基于 FPGA 的 MPEG-4 编解码器(07-18)

- CPLD与绝对式编码器在高精度高速伺服单元中的应用(07-28)

- CPLD在射频卡读写器中的应用(08-02)

- 一种基于CPLD的曼彻斯特编解码器设计(08-06)