JPEG2000中嵌入式块编码的FPGA设计

时间:09-16

来源:互联网

点击:

2 硬件设计

根据本文设计的编码算法,可用如图5所示的硬件结构实现嵌入式块编码器。

上述结构中,状态机用于控制总体的编码流程,外部信号START使状态机进入初始的预处理状态,表示此时外部RAM的数据已经准备好,然后在编码过程中根据计数器的数值进行状态切换。

设计中用到的计数器共3个,即Countrow(位计数器)、Count(列计数器)、Countloop(编码带计数器)。图6中示出了块编码器的总体流程,从中可以看出编码器的状态随计数器的数值变化的情况。

预处理单元预处理包括部分:码块预处理和位平面预处理。其中码块预处理包括计算需要编码的位平面数,撮各个系数的符号位填充相应的符号缓存,初始化显著信息缓存和细化缓存(全部清0);位平面预处理则提取当前位平面的幅度位填充相应的幅度缓存,初始化访问信息缓存(全部清0)。

读写控制控制单元负责产生合适的控制信号与外部RAM和内部缓存接口;在预处理时负责外部RAM和内部缓存的读写控制,在编码过程中则负责内部缓存和寄存器组的读写控制。

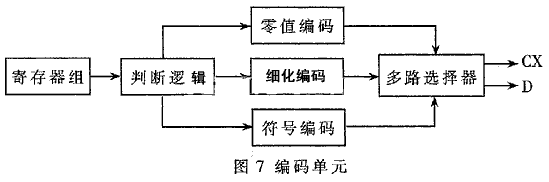

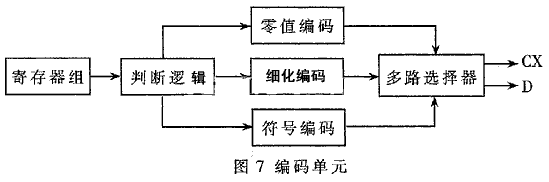

编码单元分为两部分(见图7),判断逻辑和编码操作单元。判断逻辑负责决策当前系数位是否属于当前的编码通道,编码操作单元包括零值编码、细化编码和符号编码,而流程编码则采用硬连线编码,不使用独立的单元。这几个编码操作单元直接采用组合逻辑实现,而不是采用查表方式。多路选择器则根据当前执行的编码操作选择输出合适的CX和D。

FIFO单元用于解决块编码和算术编码逻辑之间的异步问题(因为前者产生数据具有间歇性,且算术编码处理数据也会有一定的延迟)。

3 结论与展望

本文通过对嵌入式块编码的算法分析,采用了比较合理的存储结构来存储编码信息,并设计相应的寄存器组和地址产生控制逻辑,本设计能够做到读写操作无冗余信息。

本编码器算法采用MODELSIM进行功能仿真,图8是在MODELSIM中截取的部分仿真波形。仿真所采用的时钟频率是50MHz,从图8中可以看出编码过程在1074090ns完成,大约1ms左右完成32×32码块的编码。因此,对于一帧512×512的灰度图像,估计能够在0.256s内完成编码。本设计选用的FPGA芯片最高时钟频率可达到275MHz,估计通过一定的优化,可使工作频率进一步提高;另外,块编码的算法本身就蕴含着并行的特性,可以在FPGA中实现多个块编码器单元同时处理多个码块的数据,这样编码一帧图像的速度可以进一步提高。

根据本文设计的编码算法,可用如图5所示的硬件结构实现嵌入式块编码器。

上述结构中,状态机用于控制总体的编码流程,外部信号START使状态机进入初始的预处理状态,表示此时外部RAM的数据已经准备好,然后在编码过程中根据计数器的数值进行状态切换。

设计中用到的计数器共3个,即Countrow(位计数器)、Count(列计数器)、Countloop(编码带计数器)。图6中示出了块编码器的总体流程,从中可以看出编码器的状态随计数器的数值变化的情况。

预处理单元预处理包括部分:码块预处理和位平面预处理。其中码块预处理包括计算需要编码的位平面数,撮各个系数的符号位填充相应的符号缓存,初始化显著信息缓存和细化缓存(全部清0);位平面预处理则提取当前位平面的幅度位填充相应的幅度缓存,初始化访问信息缓存(全部清0)。

读写控制控制单元负责产生合适的控制信号与外部RAM和内部缓存接口;在预处理时负责外部RAM和内部缓存的读写控制,在编码过程中则负责内部缓存和寄存器组的读写控制。

编码单元分为两部分(见图7),判断逻辑和编码操作单元。判断逻辑负责决策当前系数位是否属于当前的编码通道,编码操作单元包括零值编码、细化编码和符号编码,而流程编码则采用硬连线编码,不使用独立的单元。这几个编码操作单元直接采用组合逻辑实现,而不是采用查表方式。多路选择器则根据当前执行的编码操作选择输出合适的CX和D。

FIFO单元用于解决块编码和算术编码逻辑之间的异步问题(因为前者产生数据具有间歇性,且算术编码处理数据也会有一定的延迟)。

3 结论与展望

本文通过对嵌入式块编码的算法分析,采用了比较合理的存储结构来存储编码信息,并设计相应的寄存器组和地址产生控制逻辑,本设计能够做到读写操作无冗余信息。

本编码器算法采用MODELSIM进行功能仿真,图8是在MODELSIM中截取的部分仿真波形。仿真所采用的时钟频率是50MHz,从图8中可以看出编码过程在1074090ns完成,大约1ms左右完成32×32码块的编码。因此,对于一帧512×512的灰度图像,估计能够在0.256s内完成编码。本设计选用的FPGA芯片最高时钟频率可达到275MHz,估计通过一定的优化,可使工作频率进一步提高;另外,块编码的算法本身就蕴含着并行的特性,可以在FPGA中实现多个块编码器单元同时处理多个码块的数据,这样编码一帧图像的速度可以进一步提高。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)