基于FPGA的图像预处理系统

时间:09-14

来源:互联网

点击:

图像预处理系统的实现

用标准化硬件描述语言VHDL建立FPGA模块实现。按照自顶向下的设计方法生成各设计阶层,将设计任务分解为不同的功能元件,每个元件具有专门定义的输入输出端口并执行各自的逻辑功能。该SOPC设计通过以下步骤实现。

(1)利用SOPC Builder工具编译生成用户自定制模块,调用已建立的IP模块并设置参数,配置生成片上系统;

(2)在顶层VHDL文件中调用模块并示例化,进行信号连接;

(3)对整个系统进行管脚等约束设置,全编译并进行行为和时序验证;

(4)下载和硬件调试完成。

结束语

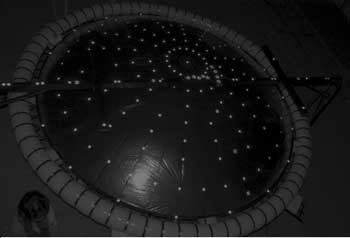

该系统对实验室在光线较弱情况下所拍的一帧3008×2000灰度图像进行对比度增强处理,处理前后如图4、5所示。在SOPC系统时钟为50MHz时,对于输入大小为3008×2000像素点的灰度图像,每一帧的处理时间为T=(1/(50×106))×3008×2000=0.120 32s。

图4 原图像

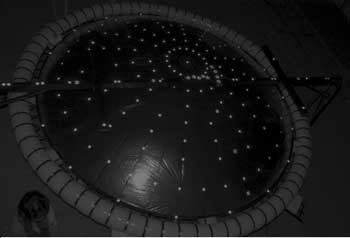

图5 处理后图像

而在3GHz Pentium 4、256MB内存的PC上通过Matlab用代码实现则需0.9850s。该设计采用FPGA实现图像预处理系统,与利用软件处理图像的方法比较起来,可以更快速地实现对图像的预处理。同时系统构成灵活,设计中模块的可重复开发性降低了生产成本、缩短了生产周期,提高了工作效率。

用标准化硬件描述语言VHDL建立FPGA模块实现。按照自顶向下的设计方法生成各设计阶层,将设计任务分解为不同的功能元件,每个元件具有专门定义的输入输出端口并执行各自的逻辑功能。该SOPC设计通过以下步骤实现。

(1)利用SOPC Builder工具编译生成用户自定制模块,调用已建立的IP模块并设置参数,配置生成片上系统;

(2)在顶层VHDL文件中调用模块并示例化,进行信号连接;

(3)对整个系统进行管脚等约束设置,全编译并进行行为和时序验证;

(4)下载和硬件调试完成。

结束语

该系统对实验室在光线较弱情况下所拍的一帧3008×2000灰度图像进行对比度增强处理,处理前后如图4、5所示。在SOPC系统时钟为50MHz时,对于输入大小为3008×2000像素点的灰度图像,每一帧的处理时间为T=(1/(50×106))×3008×2000=0.120 32s。

图4 原图像

图5 处理后图像

而在3GHz Pentium 4、256MB内存的PC上通过Matlab用代码实现则需0.9850s。该设计采用FPGA实现图像预处理系统,与利用软件处理图像的方法比较起来,可以更快速地实现对图像的预处理。同时系统构成灵活,设计中模块的可重复开发性降低了生产成本、缩短了生产周期,提高了工作效率。

DSP FPGA Altera 总线 嵌入式 Quartus VHDL 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- FPGA作为协处理器在实时系统中的应用(04-08)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)

- 基于Spartan-3A DSP的安全视频分析(05-01)