基于VHDL语言的卷积码编解码器的设计

时间:09-14

来源:互联网

点击:

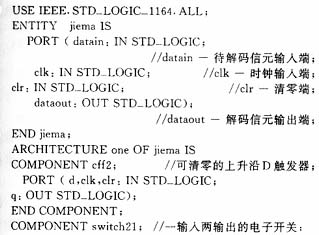

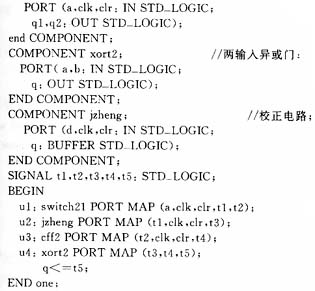

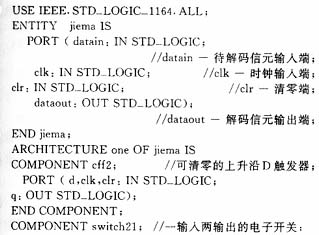

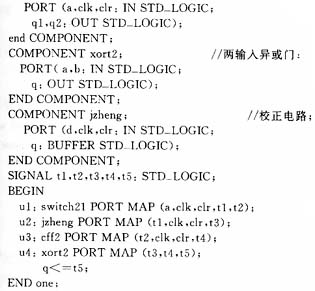

4.3卷积解码器VHDL顶层建模的VHDL端口描述

4.3.1卷积解码器各功能模块及顶层建模端口的VHDL描述

LIBRARY IEEE;

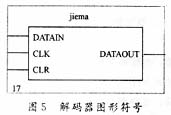

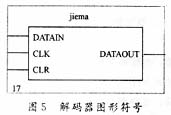

用MAX+PlusⅡ编译后生成的解码器图形符号如图5所示。

4.3.2卷积解码器VHDL顶层建模的VHDL仿真波形

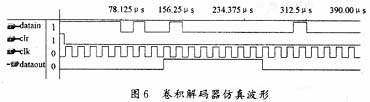

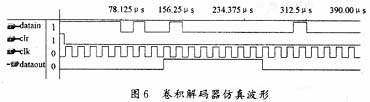

卷积解码器VHDL仿真波形如图6所示。其中待解码信元datain=“11111010010000000001” ,速率为64kP/s,对应时钟为15.625μs。仿真结果表明,解码信元输出dataout =“111 1”,相应速率为32kP/s。实际仿真还验证了当卷积解码器输入的待解码信元中有错码时的纠错情况,与理论分析结果一致。

5结语

将通过仿真的VHDL程序下载到FPGA芯片FLEX10K20上,并在实际扩频系统中用于差错控制 ,取得了较为满意的效果。

4.3.1卷积解码器各功能模块及顶层建模端口的VHDL描述

LIBRARY IEEE;

用MAX+PlusⅡ编译后生成的解码器图形符号如图5所示。

4.3.2卷积解码器VHDL顶层建模的VHDL仿真波形

卷积解码器VHDL仿真波形如图6所示。其中待解码信元datain=“11111010010000000001” ,速率为64kP/s,对应时钟为15.625μs。仿真结果表明,解码信元输出dataout =“111 1”,相应速率为32kP/s。实际仿真还验证了当卷积解码器输入的待解码信元中有错码时的纠错情况,与理论分析结果一致。

5结语

将通过仿真的VHDL程序下载到FPGA芯片FLEX10K20上,并在实际扩频系统中用于差错控制 ,取得了较为满意的效果。

编码器 VHDL EDA 解码器 FPGA 电路 Altera 仿真 CPLD 相关文章:

- 基于CPLD的开放式四轴运动控制器的设计(06-23)

- WCDMA速率适配算法的FPGA实现(07-11)

- 基于 FPGA 的 MPEG-4 编解码器(07-18)

- CPLD与绝对式编码器在高精度高速伺服单元中的应用(07-28)

- CPLD在射频卡读写器中的应用(08-02)

- 一种基于CPLD的曼彻斯特编解码器设计(08-06)