大容量串行e-Flash的FPGA配置方案

时间:09-02

来源:互联网

点击:

现场可编程门阵列FPGA(Field Programmable Gate Array)是一种集通用性强、设计灵活、集成度高和编程方便等诸多优点于一身的现场可编程ASIC。自1985年美国的Xilinx公司推出FPGA产品并取得成功以后,FPGA发展迅猛,门数不断提升,达到数百万门的规模;产品种类日益丰富,性能不断完善,在军事、通信、医疗、消费类电子等各领域发挥了巨大的作用。Xilinx公司的FPGA具有很高的性价比,其集成开发环境ISE和Webpack效率高、界面友好,因此在业界有着广泛的应用。通常对Xilinx公司的FPGA配置采用专用的配置芯片,速度较快,其价格也正逐步降低。笔者为配合某电力测量仪表的开发,对Xilinx公司的SpartanII系列FPGA的配置方案进行了探索,总结出一套成本低廉、接口简单、便于移植的方法。该方法采用Megawin公司的1Mb大容量串行e-Flash存储器MM36SB010存放FPGA配置文件,通过MCU在被动串行

模式下完成了对XC2S30的在线配置。

1 Spartanll配置简介

Xilinx公司的SpartanII系列FPGA产品成熟。该系列是采用0.18 μ m工艺的2.5V低电压FPGA芯片,功耗低,可无限次编程。XC2S30是该系列FPGA中的一款,总门数达3万门,可以实现电力测量仪表中采样数据的串行编码和多CPU间的数据交换的功能。

XC2S30采用CMOS SRAM工艺。由于SRAM的易失性,断电后配置信息消失,因此上电时必须对该芯片重新配置才能使其正常工作。本节将详细介绍XC2S30的配置方式。该配置方式对SpartanlI系列的其它FPGA同样适用。

1.1 配置模式

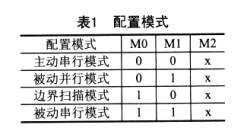

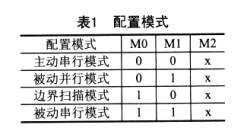

XC2S30支持4种配置模式:被动串行模式(slave serialmode)、主动串行模式(master serial mode)、被动并行模式(slave parallel mode)和边界扫描模式(boundary-scanmode)。在每次芯片上电初始化完毕后,芯片将采样模式引脚M[2:0]以决定配置模式。配置引脚状态和配置模式的关系如表1所列。(X代表任意状态。)

根据不同的应用场合,用户可以选择不同的配置方式。在XC2S30内部逻辑设计阶段,可采用边界扫描模式进行配置。配置文件可通过Xilinx公司的下载电缆(如Xilinx并行下载电缆)下载到芯片,便于在线调试。但是在产品成品阶段,已经设计好的配置文件必须存储于EEPROM或者Flash等非易失的存储器中。在系统上电时,外围器件通过FPGA配置引脚将配置文件传送至FPGA中,从而使其正常工作。根据用户的需要,可以选择主动串行模式、被动串行模式和被动并行模式。其中串行的两种模式需要的I/O口资源较少,但速度较慢;被动并行模式需要的I/O口资源较多,速度也较快。根据本系统的设计要求,选择了占用I/0口资源较少的被动串行模式对XC2$30进行配置。

1.2 被动串行模式下的配置引脚

在被动串行模式下,所用到的配置引脚为模式选择M[2:0]、配置时钟CCLK、配置复位PROGRAM、配置完成DONE、配置数据串行输入DIN和初始化状态INIT。

1.3 被动串行模式下的配置步骤及时序

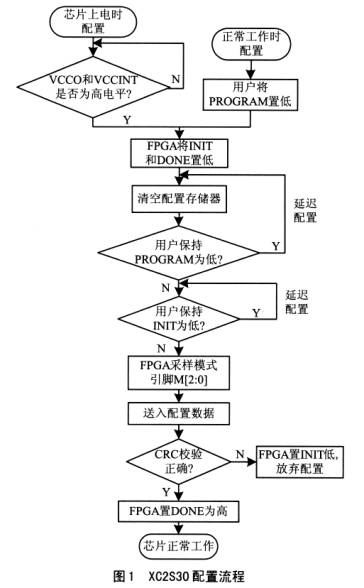

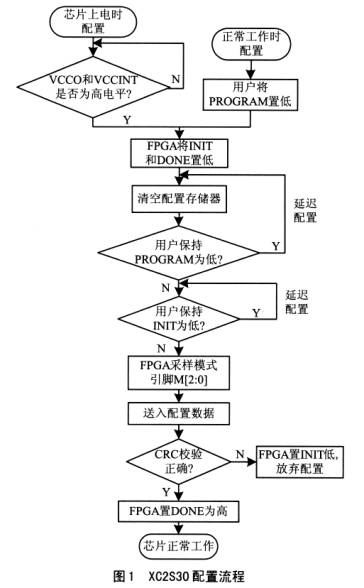

XC2S30上电后,当内核和I/O口电源引脚电压达到高电平或者用户将PROGRAM引脚置低时,芯片便进入初始化状态。此后芯片将INIT引脚置低,代表芯片正在清空配置存储器,清空完成后INIT引脚将被置高,代表清空完毕。在INIT的上升沿,模式选择引脚M[2:0]被采样,以决定配置模式,若为11x则采用被动串行模式。此后配置文件信息可以通过CCLK和DIN两个配置引脚输入至XC2S30中。配置数据在CCLK的上升沿采样。在配置期间芯片会自动进行CRC错误检验。若发生了CRC校验错误,INIT引脚将被置低,用户可以检测该引脚判断配置过程中是否出现错误。当配置文件成功输入至芯片中,芯片置DONE引脚为高,用户可检测该引脚判断配置是否成功。此后芯片进入正常工作状态。配置流程如图1所示。

2 MM36SB010的读写方式

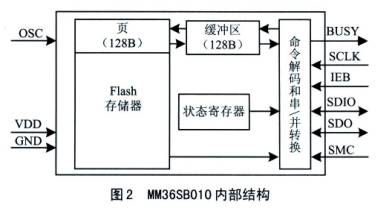

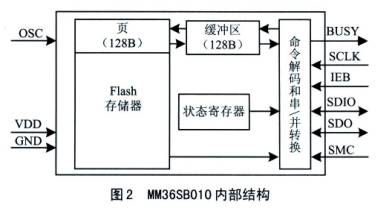

MM36SB010是Megawin公司生产的大容量SPI串行e-F1ash存储器。该芯片具有低功耗(小于4mA)、宽电压(2.4~5.5V)、高速(8MHz工作频率)、大容量(1Mb)和小页面(每页128B)、低成本等诸多优点,特别适合于消费电子、通信、工业控制等领域的应用。该芯片可工作在2线或者3线串行总线方式。本方案使用该芯片存储FPGA配置文件,读写接口简单,速度快。MM36SB010的容量为1Mb,共分1024页,每页128B。芯片内部有1个128B的缓冲区,可以对读写数据进行暂存,内部结构如图2所示。

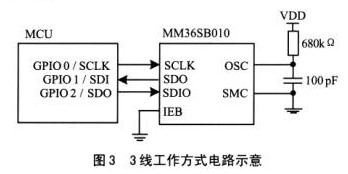

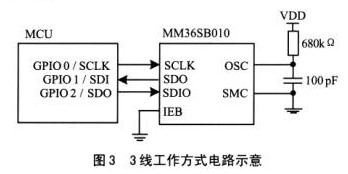

MM36SB010可工作在2线或者3线串行总线方式,工作方式通过SMC(串行模式控制)引脚来选择。当SMC为高电平时,为2线方式;当SMC为低电平时,为3线方式。本方案采用3线方式,串行数据输入和输出引脚分开,数据输入引脚为SDl0,数据输出引脚为SDO。MM36SB010的状态可通过引脚BUSY来检测,也可以通过访问状态寄存器进行查询。3线工作方式的电路示意如图3所示。

MCU可通过SCLK和SDIO引脚向MM36SB010发送控制命令,实现MM36SB010的软件复位、Flash存储器或缓冲区数据的读写和状态查询等功能。常用的命令有软件复位(SRC)、读状态寄存器(RSE)、读F1ash存储器数据(RME、RMEC)、写缓冲区(WEB、WEBC)、带预擦除功能的写缓冲区数据至Flash存储器(WBMEP)。所有的命令、地址和数据都从最低位(LSB)开始发送。在MM36SB010上电后需执行一次软件复位指令,等待20ms后芯片即可正常工作。数据可从Flash存储器中用RME和RMEC:指令直接读取,但写数据至Flash存储器前必须用WEB和WEBC命令将数据送入缓冲区内,再用WBMEP或者WBMP命令将缓冲区内的数据送入Flash存储器。

虽然MM36SB010的时钟SCLK的频率最高可达8MHz,但是由于每次从Flash读写一个字节数据前必须先送入控制命令,因此实际的读写速度小于4MHz。

模式下完成了对XC2S30的在线配置。

1 Spartanll配置简介

Xilinx公司的SpartanII系列FPGA产品成熟。该系列是采用0.18 μ m工艺的2.5V低电压FPGA芯片,功耗低,可无限次编程。XC2S30是该系列FPGA中的一款,总门数达3万门,可以实现电力测量仪表中采样数据的串行编码和多CPU间的数据交换的功能。

XC2S30采用CMOS SRAM工艺。由于SRAM的易失性,断电后配置信息消失,因此上电时必须对该芯片重新配置才能使其正常工作。本节将详细介绍XC2S30的配置方式。该配置方式对SpartanlI系列的其它FPGA同样适用。

1.1 配置模式

XC2S30支持4种配置模式:被动串行模式(slave serialmode)、主动串行模式(master serial mode)、被动并行模式(slave parallel mode)和边界扫描模式(boundary-scanmode)。在每次芯片上电初始化完毕后,芯片将采样模式引脚M[2:0]以决定配置模式。配置引脚状态和配置模式的关系如表1所列。(X代表任意状态。)

根据不同的应用场合,用户可以选择不同的配置方式。在XC2S30内部逻辑设计阶段,可采用边界扫描模式进行配置。配置文件可通过Xilinx公司的下载电缆(如Xilinx并行下载电缆)下载到芯片,便于在线调试。但是在产品成品阶段,已经设计好的配置文件必须存储于EEPROM或者Flash等非易失的存储器中。在系统上电时,外围器件通过FPGA配置引脚将配置文件传送至FPGA中,从而使其正常工作。根据用户的需要,可以选择主动串行模式、被动串行模式和被动并行模式。其中串行的两种模式需要的I/O口资源较少,但速度较慢;被动并行模式需要的I/O口资源较多,速度也较快。根据本系统的设计要求,选择了占用I/0口资源较少的被动串行模式对XC2$30进行配置。

1.2 被动串行模式下的配置引脚

在被动串行模式下,所用到的配置引脚为模式选择M[2:0]、配置时钟CCLK、配置复位PROGRAM、配置完成DONE、配置数据串行输入DIN和初始化状态INIT。

1.3 被动串行模式下的配置步骤及时序

XC2S30上电后,当内核和I/O口电源引脚电压达到高电平或者用户将PROGRAM引脚置低时,芯片便进入初始化状态。此后芯片将INIT引脚置低,代表芯片正在清空配置存储器,清空完成后INIT引脚将被置高,代表清空完毕。在INIT的上升沿,模式选择引脚M[2:0]被采样,以决定配置模式,若为11x则采用被动串行模式。此后配置文件信息可以通过CCLK和DIN两个配置引脚输入至XC2S30中。配置数据在CCLK的上升沿采样。在配置期间芯片会自动进行CRC错误检验。若发生了CRC校验错误,INIT引脚将被置低,用户可以检测该引脚判断配置过程中是否出现错误。当配置文件成功输入至芯片中,芯片置DONE引脚为高,用户可检测该引脚判断配置是否成功。此后芯片进入正常工作状态。配置流程如图1所示。

2 MM36SB010的读写方式

MM36SB010是Megawin公司生产的大容量SPI串行e-F1ash存储器。该芯片具有低功耗(小于4mA)、宽电压(2.4~5.5V)、高速(8MHz工作频率)、大容量(1Mb)和小页面(每页128B)、低成本等诸多优点,特别适合于消费电子、通信、工业控制等领域的应用。该芯片可工作在2线或者3线串行总线方式。本方案使用该芯片存储FPGA配置文件,读写接口简单,速度快。MM36SB010的容量为1Mb,共分1024页,每页128B。芯片内部有1个128B的缓冲区,可以对读写数据进行暂存,内部结构如图2所示。

MM36SB010可工作在2线或者3线串行总线方式,工作方式通过SMC(串行模式控制)引脚来选择。当SMC为高电平时,为2线方式;当SMC为低电平时,为3线方式。本方案采用3线方式,串行数据输入和输出引脚分开,数据输入引脚为SDl0,数据输出引脚为SDO。MM36SB010的状态可通过引脚BUSY来检测,也可以通过访问状态寄存器进行查询。3线工作方式的电路示意如图3所示。

MCU可通过SCLK和SDIO引脚向MM36SB010发送控制命令,实现MM36SB010的软件复位、Flash存储器或缓冲区数据的读写和状态查询等功能。常用的命令有软件复位(SRC)、读状态寄存器(RSE)、读F1ash存储器数据(RME、RMEC)、写缓冲区(WEB、WEBC)、带预擦除功能的写缓冲区数据至Flash存储器(WBMEP)。所有的命令、地址和数据都从最低位(LSB)开始发送。在MM36SB010上电后需执行一次软件复位指令,等待20ms后芯片即可正常工作。数据可从Flash存储器中用RME和RMEC:指令直接读取,但写数据至Flash存储器前必须用WEB和WEBC命令将数据送入缓冲区内,再用WBMEP或者WBMP命令将缓冲区内的数据送入Flash存储器。

虽然MM36SB010的时钟SCLK的频率最高可达8MHz,但是由于每次从Flash读写一个字节数据前必须先送入控制命令,因此实际的读写速度小于4MHz。

FPGA Xilinx 电子 MCU 电压 CMOS 总线 电路 嵌入式 C语言 单片机 ARM 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)