嵌入1-Wire主机

时间:08-31

来源:互联网

点击:

1-Wire主机DS1WM,称作1WM,创建它是为了便于实现主机CPU通过1-Wire总线与器件进行通信,而无须涉及位时序操作。本应用指南阐述如何将1-Wire主机(1WM)嵌入到用户ASIC设计之中。本文提到的DS89C200只是一个理论上的微控制器,另外,假定读者已经具备了1-Wire主机DS1WM和1-Wire协议的一般知识。如欲了解更详细信息,请参阅 Book of Button Standards和 DS1WM数据资料。

结构

DS1WM排列象一个顶级的甲胄,连接四个子模块,构成一个完整的单元。在这个顶级的甲胄中并没有HDL代码。四个子模块分别是:one_wire_interface、one_wire_master 、clk_prescaler和one_wire_io。对于那些不需要时钟分频器的应用,如果提供外部1MHZ时钟源作为clk_1us 时钟信号,就可以省去预分频器模块(如DS1WM数据资料中的τ注释,输入时钟指定在0.8MHz至1.0MHz之间)。

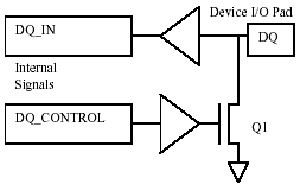

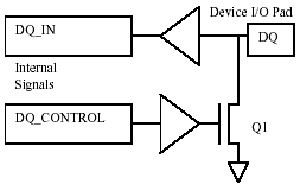

单总线输入输出模块为DATA总线和DQ提供双向信号。在大多数应用中,DQ信号是一个I/O引脚。如果是这种情况,DQ引脚驱动器必须是一个漏极开路引脚,且具有合适的ESD保护(参见图1)。另外,如果外围器件所使用的上拉电压高于1WM电源电压,则引脚驱动器还必须承受这样的超限电压,且不能使用钳位二极管。Dallas建议采用输出阻抗100Ω的驱动器(Q1),以及一个4.7kΩ的外部DQ上拉电阻至芯片VCC。为保证芯片能够正常工作,芯片VCC必须高于1-Wire从器件的高电平门限VIH。

图1:DQ驱动(one_wire_io)

程序库

Verilog源程序的编译无需外部库文件,而VHDL源程序则需要IEEE.std_logic_1164和work.std_arith库文件。

连接

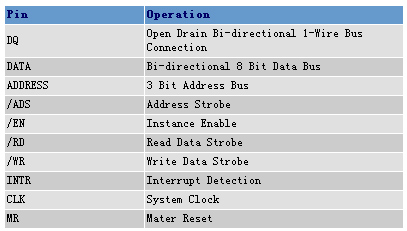

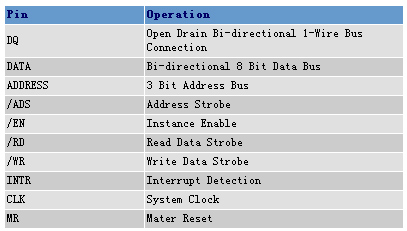

下表列出了1 - Wire主机正常工作需要连接的引线。

如果系统没有地址选通信号,/ADS可以接为低电平,使地址锁存器直通。/EN信号应由地址译码逻辑产生,在外部连接至1-Wire主机模块。如果1WM是数据总线上唯一的器件,则/EN可以接为低电平。连到CLK上的系统时钟频率必须在3.2MHz到128MHz之间。关于详细的连接操作,请参考 DS1WM11-Wire Master datasheet。

例程

下面是如何采用Verilog语言创建1-Wire主机例程的一个实例。

xcpu产生的所有信号都满足1-Wire主机的时间要求。由于在数据总线上不存在其他可寻址逻辑,所以/EN_就接为低电平。DQ_OUT信号直接连接至一个I/O引脚。 合成

该设计的合成非常简单明了。建议采用自下而上的方法分别编译各个子模块,然后有选择地在顶层进行编译。系统时钟信号和1us时钟信号必须考虑一定的时序要求,异步控制信号如/WR、/EN、/ADS和MR也需要满足一定的时序要求,clk_1us可能所需要的额外要求是不要在时钟信号上插入缓冲器。在大多数情况下需要采用某种时钟分配方案,如树型结构时钟。

资源包括:源代码、实例合成脚本以及Synopsys设计编译器一起使用的Makefile文件。为了调用这些资源,有必要创建一个.synopsys_dc.setup文件,以定义目标合成库文件。除此之外,还需要修改包含环境文件(名为"environment"),以指定器件所采用的目标库文件,从而指定输出驱动能力和输入负载。这些实例脚本是非常粗略的,而实际的脚本和约束文件将由工程师创建,以满足特定设计的时序要求。有必要提醒一下:1-Wire主机单元中的时序在设计上无法保证完全同步,这是因为DQ输出同步于CLK信号,而总线时序仅在CPU使用CLK时钟来产生/RD和/ADS信号时,才同步于CLK。

本例设计是完全独立的,已经被成功编译为FPGA和ASIC的目标文件。当面向一个典型的ASIC目标库文件合成时,本设计使用大约110个触发器、3个锁存器和1492个逻辑门。

结构

DS1WM排列象一个顶级的甲胄,连接四个子模块,构成一个完整的单元。在这个顶级的甲胄中并没有HDL代码。四个子模块分别是:one_wire_interface、one_wire_master 、clk_prescaler和one_wire_io。对于那些不需要时钟分频器的应用,如果提供外部1MHZ时钟源作为clk_1us 时钟信号,就可以省去预分频器模块(如DS1WM数据资料中的τ注释,输入时钟指定在0.8MHz至1.0MHz之间)。

单总线输入输出模块为DATA总线和DQ提供双向信号。在大多数应用中,DQ信号是一个I/O引脚。如果是这种情况,DQ引脚驱动器必须是一个漏极开路引脚,且具有合适的ESD保护(参见图1)。另外,如果外围器件所使用的上拉电压高于1WM电源电压,则引脚驱动器还必须承受这样的超限电压,且不能使用钳位二极管。Dallas建议采用输出阻抗100Ω的驱动器(Q1),以及一个4.7kΩ的外部DQ上拉电阻至芯片VCC。为保证芯片能够正常工作,芯片VCC必须高于1-Wire从器件的高电平门限VIH。

图1:DQ驱动(one_wire_io)

程序库

Verilog源程序的编译无需外部库文件,而VHDL源程序则需要IEEE.std_logic_1164和work.std_arith库文件。

连接

下表列出了1 - Wire主机正常工作需要连接的引线。

如果系统没有地址选通信号,/ADS可以接为低电平,使地址锁存器直通。/EN信号应由地址译码逻辑产生,在外部连接至1-Wire主机模块。如果1WM是数据总线上唯一的器件,则/EN可以接为低电平。连到CLK上的系统时钟频率必须在3.2MHz到128MHz之间。关于详细的连接操作,请参考 DS1WM11-Wire Master datasheet。

例程

下面是如何采用Verilog语言创建1-Wire主机例程的一个实例。

xcpu产生的所有信号都满足1-Wire主机的时间要求。由于在数据总线上不存在其他可寻址逻辑,所以/EN_就接为低电平。DQ_OUT信号直接连接至一个I/O引脚。 合成

该设计的合成非常简单明了。建议采用自下而上的方法分别编译各个子模块,然后有选择地在顶层进行编译。系统时钟信号和1us时钟信号必须考虑一定的时序要求,异步控制信号如/WR、/EN、/ADS和MR也需要满足一定的时序要求,clk_1us可能所需要的额外要求是不要在时钟信号上插入缓冲器。在大多数情况下需要采用某种时钟分配方案,如树型结构时钟。

资源包括:源代码、实例合成脚本以及Synopsys设计编译器一起使用的Makefile文件。为了调用这些资源,有必要创建一个.synopsys_dc.setup文件,以定义目标合成库文件。除此之外,还需要修改包含环境文件(名为"environment"),以指定器件所采用的目标库文件,从而指定输出驱动能力和输入负载。这些实例脚本是非常粗略的,而实际的脚本和约束文件将由工程师创建,以满足特定设计的时序要求。有必要提醒一下:1-Wire主机单元中的时序在设计上无法保证完全同步,这是因为DQ输出同步于CLK信号,而总线时序仅在CPU使用CLK时钟来产生/RD和/ADS信号时,才同步于CLK。

本例设计是完全独立的,已经被成功编译为FPGA和ASIC的目标文件。当面向一个典型的ASIC目标库文件合成时,本设计使用大约110个触发器、3个锁存器和1492个逻辑门。

总线 电压 二极管 电阻 Verilog VHDL FPGA 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA 重复配置和测试的实现(08-14)

- 经I/O优化的FPGA(04-23)

- 基于Actel FPGA的PWM IP的应用(09-17)