基于片上系统的NO.7信令采集终端的设计

时间:08-20

来源:互联网

点击:

1 引言

七号信令网是电信网的三大支撑网之一,是电信网的重要组成部分。目前,我国已经建 立了由高级信令转接点(HSTP)、低级信令转接点(LSTP)和大量的信令点(SP)组成的 三级七号信令网,使得七号信令网真正成为电信网的神经网和支撑网。因此,七号信令网的 运行质量直接影响到电信网及其各种业务网的运行稳定性和实际效益。为了保证七号信令网 的正常高效运行,七号信令集中监测系统作为对七号信令网进行集中监测和管理的工具就显 得格外重要。它根据采集到的七号MTP 二层链路消息和三层网络管理消息判别信令链路当 前状态(正常、拥塞、故障)并综合得出信令网运行状态拓朴图,而本文主要介绍的是使用 FPGA 片上系统设计一个实现采集信令消息的采集终端。

2 系统结构

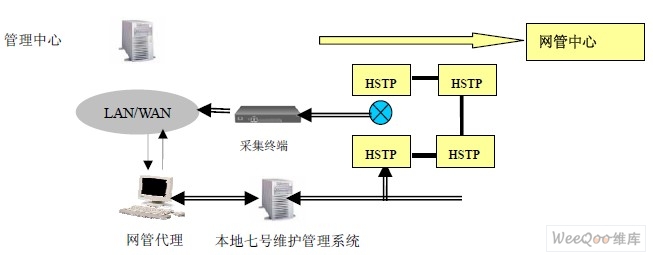

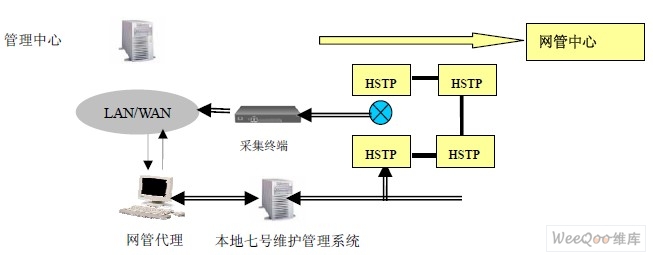

七号信令网监测管理系统由信令监测和维护管理两大部分组成,两部分逻辑功能独立, 但物理上一般采取统一平台方式。信令监测子系统提供七号信令网运行状态监视和信令数据 的采集、测试、分析处理功能。

图1 系统体系结构

2.1 终端的基本需求

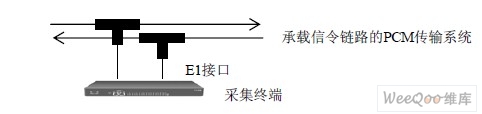

采集终端负责七号信令数据的实时采集,它通过高阻隔离头将工作的七号链路信号采集 后,通过E1 输入输出板放大,由七号信令处理板上的PMC4354 接收,送入MPC680 处理 机进行分析处理,然后由采集终端通过100M 以太网接入七号监测管理服务器。

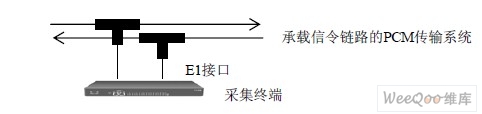

图2 信令链路高阻跨接采集方式

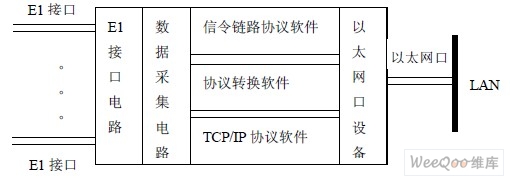

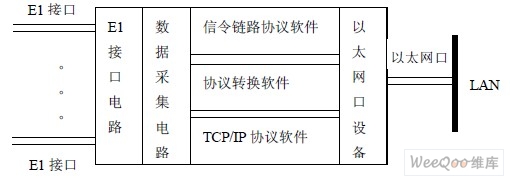

采集终端由 MPC860、E1 接口电路、数据采集电路、以太网接口设备等硬件部分和七号信令MTP 二、三层协议软件组成。

图 3 采集终端功能框图

采集终端的具体设计由E1 输入输出板、七号信令处理板、电源板等组成, 采集终端采用19 英寸的CPCI 结构,七号信令处理板前插入机框,E1 输入输出板后插 入机框,采集终端所需的同轴电缆插座,100M 以太网RJ45 插座,RS232 串口插座,防雷保 护、终端自测电路全部在E1 输入输出板。

七号信令处理板分为以下几个部分:主处理器MPC860(FPGA 内嵌),HDLC 控制器,E1 接口模块PMC4354,系统逻辑交换控制单元FPGA 和电源模块,四片PMC4354 实现16 个 E1 的接收及发送,1 个512K 的BOOTFLASK,1 个4M 的程序FLASH,2 片HY57V281620 组成32 位16M 字节的SDRAM,2 个100M 的以太网接口。

3 FPGA 处理模块

3.1 FPGA 硬件部分

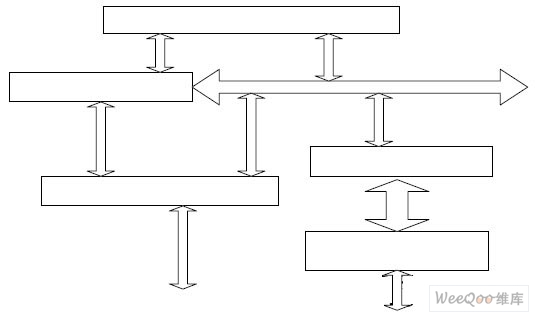

图4 FPGA 内部设计逻辑流程图

3.1.1 总体流程

信令网的七号链路通过高阻隔离头接收后,送入输入输出板,经增益放大调整、阻抗转 换后,送入七号信令处理板的PMC4354 接收,由FPGA 内部的DSN 模块完成8M 到2M 的 速率转换,实现16 个E1 到2 个E1 的交叉连接及时隙交换。具体而言,若16 个E1 全部为 接收,则实现4 个8M(512 时隙,输入)到2 个HDLC(SCC2、SCC3 共64 个时隙的交换, 输出),具体操作由CPU 的控制来实现,然后送入FPGA 内嵌MPC860 的HDLC SCC2、 SCC3 进行信令处理,处理完毕后,由MPC860 的100M 以太网SCC1 送到系统服务器。

3.1.2 逻辑部分

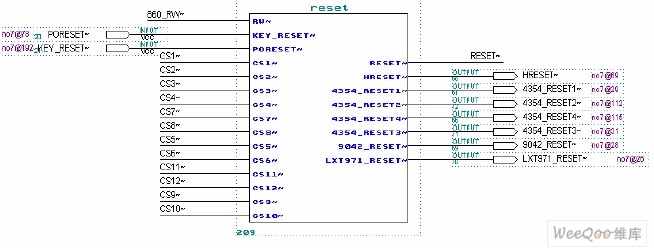

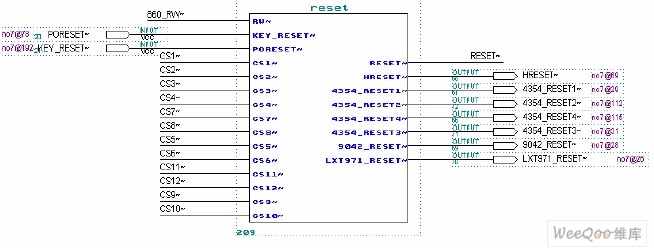

FPGA 中还需要实现以下的两个外围模块: 复位模块:系统硬复位、各个器件(4 片PM4354、1 片MT9042、1 片LXT971 的软复位); 复位部分的设计,可以对所有的芯片完成硬复位,也可以根据要求,对某一个器件来完成软 复位;

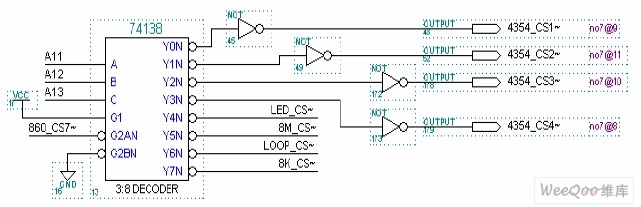

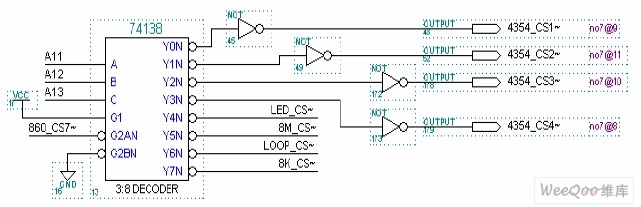

地址译码模块:完成4 片PM4354 地址译码以及片选部分的译码电路设计

3.2 FPGA 片上CPU860 软件设计

3.2.1 运行过程

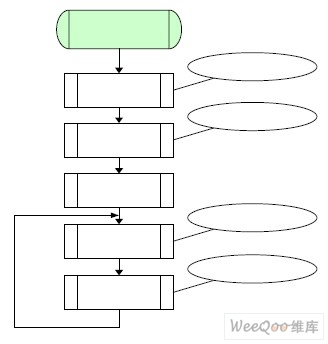

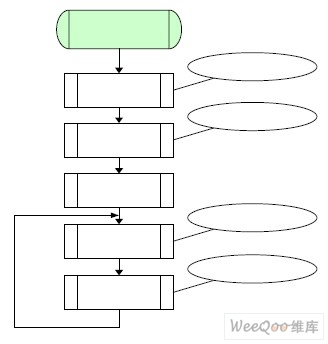

采集终端软件固化在Flash 上,终端上电后,首先运行初始引导程序,完成板级的初始 化工作,然后将操作系统装入内存并执行,操作系统最后将应用程序装入内存并启动。应用 程序即是上面介绍的四大模块,首先运行的是硬件初始化和软件初始化程序,然后进入主控 循环。循环主要是两部分:链路扫描完成端口状态的监测和链路数据的采集和发送,通信扫 描完成配置和管理命令的接收、分析和受理。链路扫描和通信接口扫描周而复始地执行,直 到系统复位重启,又从引导开始运行。

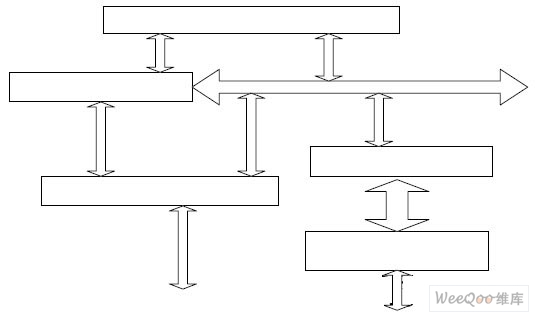

3.2.2 系统逻辑流程

4 结束语

本文论述了基于大容量 FPGA 片上系统设计并实现NO.7 信令采集终端的设计。这样 得到的具有大功能的芯片只需要少量改动就可以应用到不同的场合中,比如在基于其他信令 的监测系统中。具有广阔的应用前景。

七号信令网是电信网的三大支撑网之一,是电信网的重要组成部分。目前,我国已经建 立了由高级信令转接点(HSTP)、低级信令转接点(LSTP)和大量的信令点(SP)组成的 三级七号信令网,使得七号信令网真正成为电信网的神经网和支撑网。因此,七号信令网的 运行质量直接影响到电信网及其各种业务网的运行稳定性和实际效益。为了保证七号信令网 的正常高效运行,七号信令集中监测系统作为对七号信令网进行集中监测和管理的工具就显 得格外重要。它根据采集到的七号MTP 二层链路消息和三层网络管理消息判别信令链路当 前状态(正常、拥塞、故障)并综合得出信令网运行状态拓朴图,而本文主要介绍的是使用 FPGA 片上系统设计一个实现采集信令消息的采集终端。

2 系统结构

七号信令网监测管理系统由信令监测和维护管理两大部分组成,两部分逻辑功能独立, 但物理上一般采取统一平台方式。信令监测子系统提供七号信令网运行状态监视和信令数据 的采集、测试、分析处理功能。

图1 系统体系结构

2.1 终端的基本需求

采集终端负责七号信令数据的实时采集,它通过高阻隔离头将工作的七号链路信号采集 后,通过E1 输入输出板放大,由七号信令处理板上的PMC4354 接收,送入MPC680 处理 机进行分析处理,然后由采集终端通过100M 以太网接入七号监测管理服务器。

图2 信令链路高阻跨接采集方式

采集终端由 MPC860、E1 接口电路、数据采集电路、以太网接口设备等硬件部分和七号信令MTP 二、三层协议软件组成。

图 3 采集终端功能框图

采集终端的具体设计由E1 输入输出板、七号信令处理板、电源板等组成, 采集终端采用19 英寸的CPCI 结构,七号信令处理板前插入机框,E1 输入输出板后插 入机框,采集终端所需的同轴电缆插座,100M 以太网RJ45 插座,RS232 串口插座,防雷保 护、终端自测电路全部在E1 输入输出板。

七号信令处理板分为以下几个部分:主处理器MPC860(FPGA 内嵌),HDLC 控制器,E1 接口模块PMC4354,系统逻辑交换控制单元FPGA 和电源模块,四片PMC4354 实现16 个 E1 的接收及发送,1 个512K 的BOOTFLASK,1 个4M 的程序FLASH,2 片HY57V281620 组成32 位16M 字节的SDRAM,2 个100M 的以太网接口。

3 FPGA 处理模块

3.1 FPGA 硬件部分

图4 FPGA 内部设计逻辑流程图

3.1.1 总体流程

信令网的七号链路通过高阻隔离头接收后,送入输入输出板,经增益放大调整、阻抗转 换后,送入七号信令处理板的PMC4354 接收,由FPGA 内部的DSN 模块完成8M 到2M 的 速率转换,实现16 个E1 到2 个E1 的交叉连接及时隙交换。具体而言,若16 个E1 全部为 接收,则实现4 个8M(512 时隙,输入)到2 个HDLC(SCC2、SCC3 共64 个时隙的交换, 输出),具体操作由CPU 的控制来实现,然后送入FPGA 内嵌MPC860 的HDLC SCC2、 SCC3 进行信令处理,处理完毕后,由MPC860 的100M 以太网SCC1 送到系统服务器。

3.1.2 逻辑部分

FPGA 中还需要实现以下的两个外围模块: 复位模块:系统硬复位、各个器件(4 片PM4354、1 片MT9042、1 片LXT971 的软复位); 复位部分的设计,可以对所有的芯片完成硬复位,也可以根据要求,对某一个器件来完成软 复位;

地址译码模块:完成4 片PM4354 地址译码以及片选部分的译码电路设计

3.2 FPGA 片上CPU860 软件设计

3.2.1 运行过程

采集终端软件固化在Flash 上,终端上电后,首先运行初始引导程序,完成板级的初始 化工作,然后将操作系统装入内存并执行,操作系统最后将应用程序装入内存并启动。应用 程序即是上面介绍的四大模块,首先运行的是硬件初始化和软件初始化程序,然后进入主控 循环。循环主要是两部分:链路扫描完成端口状态的监测和链路数据的采集和发送,通信扫 描完成配置和管理命令的接收、分析和受理。链路扫描和通信接口扫描周而复始地执行,直 到系统复位重启,又从引导开始运行。

3.2.2 系统逻辑流程

4 结束语

本文论述了基于大容量 FPGA 片上系统设计并实现NO.7 信令采集终端的设计。这样 得到的具有大功能的芯片只需要少量改动就可以应用到不同的场合中,比如在基于其他信令 的监测系统中。具有广阔的应用前景。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)